# **APEX 20K**

プログラマブル・ロジック・ デバイス・ファミリ

2001年3月 ver.3.4 Data Sheet

# 特長

Preliminary Information (暫定仕様)

- \*\* 業界初の system-on-a-programmable-chip (SOPC) インテグレーションを可能にしたプログラマブル・ロジック・デバイス (PLD)

- ルック・アップ・テーブル(LUT)ロジック、プロダクト・ターム・ロジック、およびエンベデッド・メモリを集積した  $MultiCore^{TM}$  アーキテクチャ

- 多数のレジスタを必要とするファンクションの実現に最適なLUTロジック

- エンベデッド・システム・ブロック (ESB) には、FIFO (First-In First-Out) バッファ、デュアル・ポート RAM、CAM (Content-Addressable Memory) を含むメモリ・ファンクションが構成可能

- 組み合わせ回路を中心にしたファンクションの実現にプロダクト・タームの使用を可能にした ESB

### ■ 高集積

- 30,000から1,500,000の標準ゲート(表1と2を参照)

- 最大51,840個のロジック・エレメント(LE)

- 提供されているロジックのリソースを減少させることなく、最大 442,368ビットまでのRAMを構成可能

- プロダクト・タームをベースにした最大3,456個のマクロセル

| 表 1. APEX        | 表 1. APEX 20K デバイスの特長 |          |          | 注 (1)     |           |          |           |  |  |  |

|------------------|-----------------------|----------|----------|-----------|-----------|----------|-----------|--|--|--|

| 機能               | EP20K30E              | EP20K60E | EP20K100 | EP20K100E | EP20K160E | EP20K200 | EP20K200E |  |  |  |

| 最大<br>システム・      | 113,000               | 162,000  | 263,000  | 263,000   | 404,000   | 526,000  | 526,000   |  |  |  |

| ゲート数<br>標準ゲート数   | 30,000                | 60,000   | 100,000  | 100,000   | 160,000   | 200,000  | 200,000   |  |  |  |

| LE数              | 1,200                 | 2,560    | 4,160    | 4,160     | 6,400     | 8,320    | 8,320     |  |  |  |

| ESB数             | 12                    | 16       | 26       | 26        | 40        | 52       | 52        |  |  |  |

| 最大 RAM<br>ビット数   | 24,576                | 32,768   | 53,248   | 53,248    | 81,920    | 106,496  | 106,496   |  |  |  |

| 最大<br>マクロセル数     | 192                   | 256      | 416      | 416       | 640       | 832      | 832       |  |  |  |

| 最大ユーザ<br>I/O ピン数 | 128                   | 196      | 252      | 246       | 316       | 382      | 376       |  |  |  |

| 表 2. APEX 20K デバイスの特長 注 (1) |           |           |           |           |            |            |  |  |

|-----------------------------|-----------|-----------|-----------|-----------|------------|------------|--|--|

| 機能                          | EP20K300E | EP20K400  | EP20K400E | EP20K600E | EP20K1000E | EP20K1500E |  |  |

| 最大システム・<br>ゲート数             | 728,000   | 1,052,000 | 1,052,000 | 1,537,000 | 1,772,000  | 2,392,000  |  |  |

| 標準ゲート数                      | 300,000   | 400,000   | 400,000   | 600,000   | 1,000,000  | 1,500,000  |  |  |

| LE数                         | 11,520    | 16,640    | 16,640    | 24,320    | 38,400     | 51,840     |  |  |

| ESB数                        | 72        | 104       | 104       | 152       | 160        | 216        |  |  |

| 最大<br>RAM ビット数              | 147,456   | 212,992   | 212,992   | 311,296   | 327,680    | 442,368    |  |  |

| 最大<br>マクロセル数                | 1,152     | 1,664     | 1,664     | 2,432     | 2,560      | 3,456      |  |  |

| 最大ユーザ<br>I/O ピン数            | 408       | 502       | 488       | 588       | 708        | 808        |  |  |

### 注:

(1) IEEE Std. 1149.1の標準規格に準拠した内蔵のJTAG (Joint Test Action Group) バウンダリ・スキャン回路がさらに最大 57,000ゲート加算しています。

# さらに多くの 特長

- ロー・パワー動作をサポート

- 1.8 V および 2.5 V の電源電圧 (表 3 を参照)

- 1.8 V、2.5 V、3.3 V、5.0 V の各デバイスとのインタフェースを可能に した MultiVolt I/O インタフェース (表3を参照)

- プログラマブルなパワー・セーブ・モードを提供するESB

| 機能                                                  | デバイス名                            |                                                                                                                                |  |  |

|-----------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                     | EP20K100<br>EP20K200<br>EP20K400 | EP20K30E<br>EP20K60E<br>EP20K100E<br>EP20K160E<br>EP20K200E<br>EP20K300E<br>EP20K400E<br>EP20K600E<br>EP20K1000E<br>EP20K1500E |  |  |

| 内部電源電圧(V <sub>CCINT</sub> )                         | 2.5 V                            | 1.8 V                                                                                                                          |  |  |

| MultiVolt I/O インタフェースの<br>電圧レベル(V <sub>CCIO</sub> ) | 2.5 V、3.3 V、5.0 V (1)            | 1.8 V、2.5 V、3.3 V、<br>5.0 V (2)                                                                                                |  |  |

### 注:

- (1)  $5.0\,\mathrm{V}$ を許容する APEX  $20\mathrm{K}$  デバイスもあります。詳細については、 $46\,\mathrm{^{\circ}}$  ページの 「MultiVolt I/Oインタフェース」を参照してください。

- (2) APEX 20KEデバイスは外部抵抗を使用することにより 5.0 V を許容可能です。

- 最大4個のPLL (Phase-Locked Loop) による柔軟性の高いクロック・マネージメント回路

- 低スキューのクロック・ツリーを内蔵

- 最大8本までのグローバル・クロック信号

- クロックの遅延とスキューを低減する ClockLock<sup>TM</sup>機能

- クロック乗算と除算を提供する ClockBoost<sup>TM</sup> 機能

- クロックの位相と遅延をプログラマブルにシフトさせることができる ClockShift<sup>TM</sup>機能

### ■ パワフルなI/O機能

- Peripheral Component Interconnect Special Interest Group (PCI SIG) の PCI Local Bus Specification, Revision 2.2 の 33 MHz または 66 MHz、32 ビットまたは64 ビットの3.3 V 動作仕様に準拠

- DDR SDRAMやZBT SRAM (ZBTは Integrated Device Technology, Inc. の商標) などの高速外部メモリのサポート

- 最大250 MHzの双方向I/Oパフォーマンス( $t_{CO} + t_{SU}$ )

- チャネルあたり最大840 MBのLVDSパフォーマンス

- I/Oピンとローカル・インタコネクトとのダイレクト接続により、複雑なロジックに対して高速の $t_{CO}$ と $t_{SU}$ を提供

- 1.8 V、2.5 V、3.3 V、および 5.0 V デバイスとのインタフェースをサポートする MultiVolt I/Oインタフェース(表3を参照)

- V<sub>CCIO</sub>へのプログラマブルなクランプ機能

- 各ピンごとに個別に設定可能なトライ・ステート出力イネーブル・コントロール

- スイッチング・ノイズを低減することができるプログラマブルな出力スルー・レート・コントロール

- LVDS (Low-Voltage Differential Signaling)、LVPECL、PCI-X、AGP、CTT、SSTL-3 (Stub-Series Terminated Logic) およびSSTL-2、GTL+(Gunning Transceiver Logic plus)、HSTLのClass I(High-Speed Terminated Logic)を含む最新の標準I/O規格をサポート

- APEX 20KE デバイスでホット・ソケッティング (活線挿抜) をサポート

- コンフィギュレーションの実行前および実行中に I/O ピンをプルアップ可能

### ■ 最新のインタコネクト構造

- 4 レベルの階層を持った配線構造となっている FastTrack® インタコネクトにより、高速で予測可能な配線遅延を実現

- アダー、カウンタ、コンパレータのような演算機能を高速で実現する専用キャリー・チェイン(ソフトウェア・ツールやメガファンクションが自動的に使用)

- 高ファン・インの論理機能を高速で実現する専用カスケード・チェイン (ソフトウェア・ツールやメガファンクションが自動的に使用)

- 1個のLEから高速のローカル・インタコネクトを通じて他の29個のLE のドライブを可能にしたインタリーブド・ローカル・インタコネクト

### ■ 最先端のパッケージ・オプション

- 144 ピンから 1,020 ピンまでの豊富なパッケージ・オプション (表 4 から7までを参照)

- ボード・スペースの効率を最大化する FineLine BGA $^{TM}$ パッケージ

### ■ 最先端ソフトウェアによるサポート

- Windows ベースの PC、Sun SPARCstation、および HP 9000 Series 700/800 のワークステーション上で動作するアルテラの Quartus<sup>TM</sup> II 開発システムによるソフトウェア・デザイン・サポートと自動配置配線

- アルテラの MegaCore® ファンクションと AMPP<sup>SM</sup>(Altera Megafunction Partners Program)メガファンクションが使用可能

- 標準的な論理合成ツール、シミュレーション・ツール、タイミング解析 ツールとの統合を実現するNativeLink<sup>TM</sup>機能

- 動作中のデバイスの内部ノードにアクセスできる Quartus II の Signal Tap TM エンベデッド・ロジック・アナライザにより、デザインの イン・システムでの評価が簡単に実現可能

- PVCS、RCS (Revision Control System)、SCCS (Source Code Control System)を含む標準的なリビジョン・コントロール・ソフトウェア・パッケージのサポート

| デバイス名      | 144ピン | 208ピン        | 240ピン        | 356ピン | 652ピン | 655ピン |

|------------|-------|--------------|--------------|-------|-------|-------|

|            | TQFP  | PQFP<br>RQFP | PQFP<br>RQFP | BGA   | BGA   | PGA   |

| EP20K30E   | 92    | 125          |              |       |       |       |

| EP20K60E   | 92    | 148          | 151          | 196   |       |       |

| EP20K100   | 101   | 159          | 189          | 252   |       |       |

| EP20K100E  | 92    | 151          | 183          | 246   |       |       |

| EP20K160E  | 88    | 143          | 175          | 271   |       |       |

| EP20K200   |       | 144          | 174          | 277   |       |       |

| EP20K200E  |       | 136          | 168          | 271   | 376   |       |

| EP20K300E  |       |              | 152          |       | 408   |       |

| EP20K400   |       |              |              |       | 502   | 502   |

| EP20K400E  |       |              |              |       | 488   |       |

| EP20K600E  |       |              |              |       | 488   |       |

| EP20K1000E |       |              |              |       | 488   |       |

| EP20K1500E |       |              |              |       | 488   |       |

| 表5. APEX 20KのFi | neLine BGAパッ | <b>,ケージのオプシ</b> ョ | ョンとI/Oピン数 | 注 (1)、(2) |         |

|-----------------|--------------|-------------------|-----------|-----------|---------|

| デバイス名           | 144ピン        | 324ピン             | 484ピン     | 672ピン     | 1,020ピン |

| EP20K30E        | 93           | 128               |           |           |         |

| EP20K60E        | 93           | 196               |           |           |         |

| EP20K100        |              | 252               |           |           |         |

| EP20K100E       | 93           | 246               |           |           |         |

| EP20K160E       |              |                   | 316       |           |         |

| EP20K200        |              |                   | 382       |           |         |

| EP20K200E       |              |                   | 376       | 376       |         |

| EP20K300E       |              |                   |           | 408       |         |

| EP20K400        |              |                   |           | 502 (3)   |         |

| EP20K400E       |              |                   |           | 488 (3)   |         |

| EP20K600E       |              |                   |           | 508 (3)   | 588     |

| EP20K1000E      |              |                   |           | 508 (3)   | 708     |

| EP20K1500E      |              |                   |           |           | 808     |

### 注:

- (1) I/O数には入力専用ピンとクロック専用ピンが含まれます。

- (2) APEX 20K デバイスには、薄型クワッド・フラット・パック (TQFP)、プラスチック・クワッド・フラット・パック (PQFP)、パワー・クワッド・フラット・パック (RQFP)、1.27mm ピッチのボール・グリッド・アレイ (BGA)、1.00mm ピッチの FineLine BGA、およびピン・グリッド・アレイ (PGA) の各パッケージが提供されています。

- ピッチの Fine Line BGA、およびピン・グリッド・アレイ (PGA) の各パッケージが提供されています。

(3) このデバイスは、通常のパッケージより背が高く、熱特性に改良されたパッケージです。パッケージの詳しいサイズ情報については、「Altera Device Package Information」のデータシートを参照してください。

| 表 6. APEX 20K QFP、BGA、PGA パッケージのサイズ |               |              |              |              |              |              |  |  |

|-------------------------------------|---------------|--------------|--------------|--------------|--------------|--------------|--|--|

| 機能                                  | 144ピン<br>TQFP | 208ピン<br>QFP | 240ピン<br>QFP | 356ピン<br>BGA | 652ピン<br>BGA | 655ピン<br>PGA |  |  |

| ピッチ (mm)                            | 0.50          | 0.50         | 0.50         | 1.27         | 1.27         | -            |  |  |

| 面積(mm <sup>2</sup> )                | 484           | 924          | 1,218        | 1,225        | 2,025        | 3,906        |  |  |

| 長さ×幅<br>(mm×mm)                     | 22 × 22       | 30.4 × 30.4  | 34.9 × 34.9  | 35 × 35      | 45 × 45      | 62.5 × 62.5  |  |  |

| 表7. APEX 20K FineLine BGA パッケージのサイズ     |       |       |         |         |         |  |  |  |

|-----------------------------------------|-------|-------|---------|---------|---------|--|--|--|

| 機能 144 ピン 324 ピン 484 ピン 672 ピン 1,020 ピン |       |       |         |         |         |  |  |  |

| ピッチ (mm)                                | 1.00  | 1.00  | 1.00    | 1.00    | 1.00    |  |  |  |

| 面積(mm²)                                 | 169   | 361   | 529     | 729     | 1,089   |  |  |  |

| 長さ×幅(mm×mm)                             | 13×13 | 19×19 | 23 × 23 | 27 × 27 | 33 × 33 |  |  |  |

# 概要

APEXTM 20K デバイスは、LUT ベースのロジック、プロダクト・ターム・ベースのロジックの長所とさらに機能強化されたメモリ構造を統合したMultiCore アーキテクチャによる業界初のPLDです。LUT をベースにしたロジックは、データ・パス、多数のレジスタを使用するファンクションや演算ファンクション、ディジタル信号処理(DSP)のデザインを最適化された性能と効率で実現します。これに対して、プロダクト・タームをベースにしたロジックを使用することで、多数のステートと遷移条件を持つステート・マシンのような複雑な組み合わせ回路のパスが最適化されます。APEX 20K デバイスのアーキテクチャは、メモリ・ファンクション、多様な MegaCore ファンクションや AMPP ファンクションと LUT およびプロダクト・タームをベースにしたロジックを組み合わせることによって、System-on-a-Programmable-Chip のデザインに適合させることができるようになっています。これにより、これまで LUT、プロダクト・ターム、そしてメモリ・ベースの各デバイスを組み合わせて使用する必要があったアプリケーションを1個の APEX 20K デバイスに集積することができます。

APEX 20KEは APEX 20K の上位互換デバイスとなっており、最新の標準I/O規格、CAM、複数の追加グローバル・クロック、さらに性能と機能が強化された ClockLockによるクロック回路などの機能が追加サポートされています。さらに、APEX 20KEデバイスはAPEX 20Kファミリの集積度を1,500,000ゲート以上にまで拡張しています。APEX 20KEデバイスには、デバイス名の最後に"E"のサフィックスが付加されます(例えば、EP20K1000Eは APEX 20KEデバイスです)。表8は、APEX 20K デバイスと APEX 20KE デバイスに提供されている機能を比較したものです。

| 機能                | APEX 20K デバイス                      | APEX 20KEデバイス                          |

|-------------------|------------------------------------|----------------------------------------|

| MultiCore システム・   | フル・サポート                            | フル・サポート                                |

| インテグレーション         |                                    |                                        |

| 活線挿抜のサポート         | -                                  | フル・サポート                                |

| SignalTapロジック解析機能 | フル・サポート                            | フル・サポート                                |

| 32 ビットまたは 64 ビット、 | – 1、– 2スピード・グレードで完全準拠              | - 1、- 2 スピード・グレードで完全準拠                 |

| 33 MHz PCI        |                                    |                                        |

| 32 ビットまたは 64 ビット、 | -                                  | - 1 スピード・グレードで完全準拠                     |

| 66 MHz PCI        |                                    |                                        |

| MultiVolt I/O     | 2.5 V または3.3 V の V <sub>CCIO</sub> | 1.8 V、2.5 V、または3.3 VのV <sub>CCIO</sub> |

|                   | V <sub>CCIO</sub> はデバイス全体でいずれかの電圧に | V <sub>CCIO</sub> はブロックごとに選択可能         |

|                   | 選択                                 | 外部抵抗を使用することで5.0 Vを許容                   |

|                   | 特定のデバイスは5.0 V を許容                  |                                        |

| 機能             | APEX 20Kデバイス                      | APEX 20KEデバイス                        |

|----------------|-----------------------------------|--------------------------------------|

| lockLock のサポート | クロック遅延の低減                         | クロック遅延の低減                            |

|                | クロック周波数の2倍と4倍の逓倍機能                | $m/(n \times v)$ によるクロック周波数の逓倍機能     |

|                |                                   | ClockLockの出力をチップ外部にドライブ可能            |

|                |                                   | 外部クロックのフィードバック                       |

|                |                                   | ClockShift                           |

|                |                                   | LVDSをサポート                            |

|                |                                   | 最大4個のPLL                             |

|                |                                   | ClockShift、クロック位相の調整                 |

| ロック専用ピンと       | 6本                                | 8本                                   |

| 力専用ピン          |                                   |                                      |

| 準I/O規格のサポート    | 2.5 V、3.3 V、5.0 V I/O             | 1.8 V、2.5 V、3.3 V、5.0 V I/O          |

|                | 3.3 V PCI                         | 2.5 V I/O                            |

|                | LVCMOS (Low-voltage complementary | 3.3 VのPCIとPCI-X                      |

|                | metal-oxide semiconductor)        | 3.3 V O AGP (Advanced Graphics Port) |

|                | LVTTL (Low-voltage transistor-to- | CTT (Center tap terminated)          |

|                | transistor logic)                 | GTL+                                 |

|                |                                   | LVCMOS                               |

|                |                                   | LVTTL                                |

|                |                                   | True-LVDS および LVPECL データ・ピン          |

|                |                                   | (EP20K300E およびそれより高集積のデバイン           |

|                |                                   | LVDSおよびLVPECLクロック・ピン(すべて             |

|                |                                   | デバイス)                                |

|                |                                   | 最大 156 MbpsのLVDSおよびLVPECLデータ         |

|                |                                   | ピン(– 1スピード・グレード・デバイス)                |

|                |                                   | HSTL Class I                         |

|                |                                   | PCI-X                                |

|                |                                   | SSTL-2 Class I & II                  |

|                |                                   | SSTL-3 Class I & II                  |

| モリ・サポート        | デュアル・ポート RAM                      | CAM                                  |

|                | FIFO                              | デュアル・ポートRAM                          |

|                | RAM                               | FIFO                                 |

|                | ROM                               | RAM                                  |

|                |                                   | ROM                                  |

APEX 20K のすべてのデバイスはリコンフィギュレーション可能となっており、 出荷前に 100%のテストが実施されています。このため、フォルト・カバレッジ を目的としたテスト・ベクタを生成する必要はありません。その代わりに、設計 者はデザインのシミュレーションとデザイン検証に注力することができます。ま た、APEX 20Kデバイスでは要求される特定の機能をボード上でコンフィギュレー ションできるため、ASIC(Application-Specific Integrated Circuit)の場合のよ うにデザインの異なるデバイスごとに在庫を管理する必要がありません。

APEX 20K デバイスは、システム電源の投入時にアルテラのシリアル・コンフィギュレーション・デバイスにストアされたデータ、またはシステム・コントローラから提供されるデータによってコンフィギュレーションされます。アルテラはイン・システム・プログラマビリティ(ISP)対応の EPC1、EPC2、および EPC16 コンフィギュレーション・デバイスを供給しており、このデバイスから APEX 20K デバイスをシリアルのデータ・ストリームでコンフィギュレーションすることができます。さらに、APEX 20K デバイスにはマイクロプロセッサとの最適化されたインタフェースが内蔵されており、マイクロプロセッサからのシリアルまたはパラレルのデータにより、APEX 20K デバイスを同期または非同期でコンフィギュレーションすることができます。このインタフェースの実現によって、マイクロプロセッサは APEX 20K デバイスをメモリとして取り扱うことができるため、バーチャルなメモリ・ロケーションにデータを書き込む動作で APEX 20K デバイスをコンフィギュレーションも容易に実行できます。

コンフィギュレーションされた APEX 20K デバイスをイン・サーキットでリセットし、新しいデータをロードすることによってリコンフィギュレーションを実行することができます。システムの動作中でもリアル・タイムの変更が可能となっているため、リコンフィギュラブル・コンピューティングなどの革新的なアプリケーションを実現することもできます。

APEX 20K デバイスは、HDL および回路図によるデザイン入力、コンパイル、論理合成、完全なシミュレーション、ワースト・ケースのタイミング解析、SignalTapロジック解析機能、デバイス・コンフィギュレーションの各機能をシングル・パッケージに統合したアルテラのQuartus II 開発システムによってサポートされています。Quartus II のソフトウェアはWindows ベースのPC、Sun SPARCstation、およびHP 9000 シリーズ 700/800 のワークステーション上で動作します。

Quartus II ソフトウェアは、PC および UNIX ワークステーションをベースにした他社の業界標準 EDA ツールとの NativeLink インタフェースを実現しています。この NativeLink インタフェースにより、ユーザはサード・パーティのデザイン・ツールから Quartus II ソフトウェアを起動することができます。さらに、Quartus II ソフトウェアには最適化された合成ライブラリが含まれており、合成ツールがこれらのライブラリを使用してデザインをAPEX 20Kに最適化できるようになっています。例えば、Quartus II 開発システムとともに供給されるシノプシス社の Design Compiler ライブラリには、APEX 20K のアーキテクチャに最適化された DesignWare ファンクションが含まれています。

# 機能の説明

APEX 20K デバイスは、LUT ベースのロジック、プロダクト・ターム・ベースのロジック、そしてメモリを1個のデバイス上に実現することができます。APEX 20K デバイス内での信号の接続は(デバイス・ピンとの接続も同様)、デバイス全体を縦横に走っている連続したロウとカラムの高速配線チャネル、FastTrack インタコネクトによって行われます。

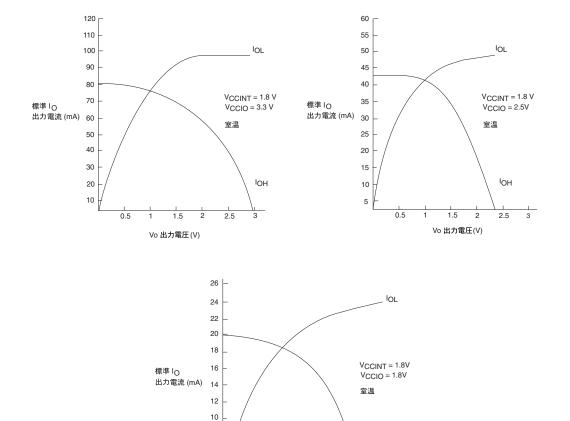

各I/Oピンはロウとカラムの FastTrack インタコネクトの先端に配置されている I/Oエレメント(IOE)と接続されます。各IOEには双方向のI/Oバッファとレジスタが 1 個ずつ内蔵されており、このレジスタは入力または出力信号、あるいは双方向信号が接続される入力レジスタまたは出力レジスタのいずれかとして使用することができます。専用のクロック・ピンを使用した場合は、これらのレジスタがこれまでにない高い性能を実現します。IOE は、 $3.3\,\mathrm{V}/64\,\mathrm{E'}$  ット /  $66\,\mathrm{MHz}$  の PCI 仕様への準拠、JTAG BST のサポート、スルー・レート・コントロール、トライ・ステート・バッファなど、多様な機能を提供しています。APEX 20KE デバイスには、 $1.8\,\mathrm{V}$  の I/O、 $2.5\,\mathrm{V}$  の I/O、LVCMOS、LVTTL、LVPECL、 $3.3\,\mathrm{V}$  の PCI、PCI-X、LVDS、GTL+、SSTL-2、SSTL-3、HSTL、CTT、 $3.3\,\mathrm{V}$  る合む標準 I/O 規格のサポートなど、さらに拡張強化された I/O 機能が提供されています。

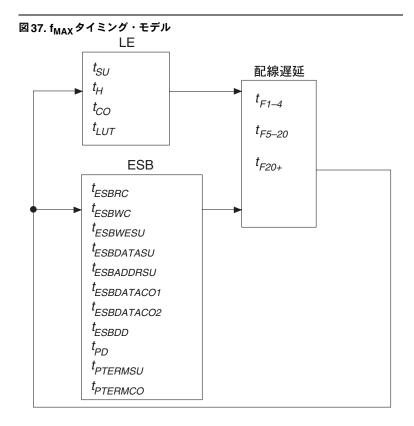

ESBには、CAM、RAM、デュアル・ポートRAM、ROM、FIFOを含む多様なメモリ・ファンクションを実現することができます。メモリをダイに直接埋め込むことによって、分散型のRAMによる実現方法よりも性能が改善され、ダイ・エリアが縮小されます。さらに、複数のESBをカスケード接続することができるため、APEX 20Kデバイスには高集積デザインに要求される複数の大容量メモリ・ブロックを構成することができます。ESBの高速性により、各ESBにはスピードを一切犠牲にすることなく、小容量の高速メモリが実現できます。また、APEX 20Kデバイスには豊富なESBが内蔵されているため、システムの要求に応じた数のメモリ・ブロックをそれぞれ異なるサイズで構成することができます。図1はAPEX 20Kデバイス内部の全体的な構造を示したものです。

### 図1. APEX 20Kデバイスのブロック図 クロック・マネージメント回路 FastTrack インタコネクト IOE ClockLock IOE データ・パス、 DSP ファンクション用・ LUT LUT LUT 4 入力 LUT IOE PCI、GTL+、 プロダクト・ターム プロダクト・ターム プロダクト・ターム プロダクト・ターム SSTL-3. LVDS 高速コントロール・-メモリ メモリ メモリ メモリ などの標準 I/O ロジック、 規格をサポート ステート・ する IOE LUT LUT マシン用プロダクト・ タームを内蔵 プロダクト・ターム プロダクト・ターム プロダクト・ターム プロダクト・ターム メモリ メモリ メモリ メモリ CAM、RAM、 ROM. FIFO および他のメモリ・ ファンクションを 含むエンベデッド・ IOE ロンー・ メモリの柔軟性に 富んだ集積化

APEX 20K デバイスには、2本のクロック専用ピンと各レジスタのコントロール入力をドライブできる 4本の入力専用ピンが提供されています。これらのピンからの信号は効率的にデバイス内部に分配され、高速で低スキューのコントロール信号となります。これらの信号の接続には、最小の遅延と低スキューを実現する専用の配線チャネルが使用されます。4本の入力専用ピンは4本のグローバル信号をドライブします。これら4本のグローバル信号は内部ロジックからドライブすることもでき、クロック・デバイダや大きなファンアウトを持つ内部生成の非同期クリア信号に対する理想的なソリューションとなっています。APEX 20K デバイスに提供されているクロック専用ピンはロジックを供給することもできます。APEX 20K デバイスは、クロック・マネージメント回路である 2ClockLock とClockBoost の回路も備えています。2APEX 20K 20

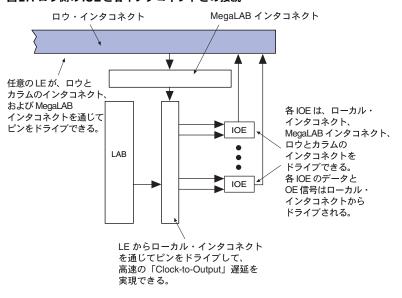

### MegaLABの構造

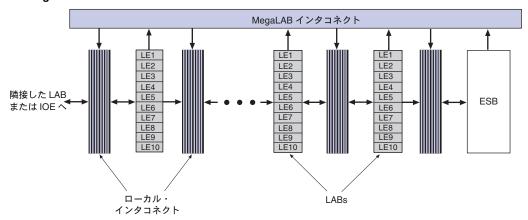

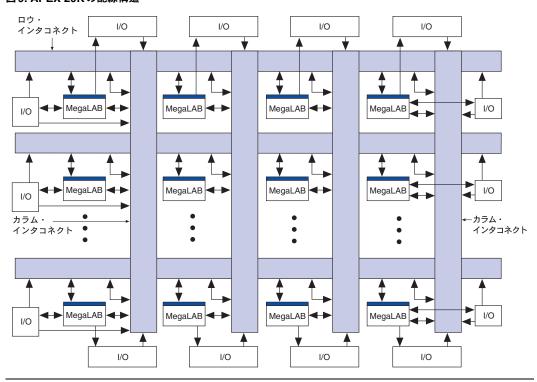

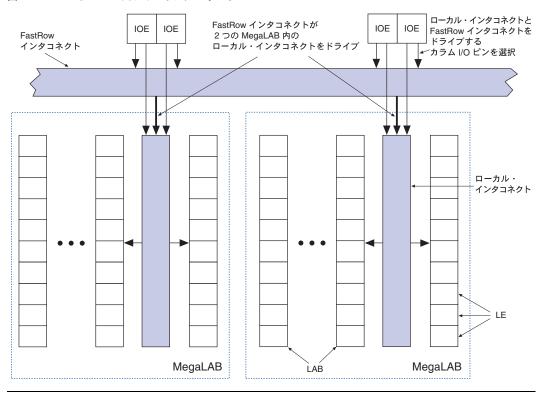

APEX 20Kデバイスは、MegaLAB<sup>TM</sup>をアレイ上に配置した構造となっています。各 MegaLABは、16個のロジック・アレイ・ブロック(LAB)、1個のESB、およびMegaLAB内の信号を接続するMegaLABインタコネクトで構成されています。EP20K1000EとEP20K1500Eの両デバイスでは、各 MegaLABに 24個の LAB が含まれています。信号は、FastTrack インタコネクトを通じて異なる MegaLAB間、および MegaLAB と I/O ピンとの間で接続されます。また、両端の LAB はローカル・インタコネクトを通じて I/O ピンから信号の入出力が可能です。図 2 は MegaLABの構造を示したものです。

### 図2. MegaLABの構造

### ロジック・アレイ・ブロック

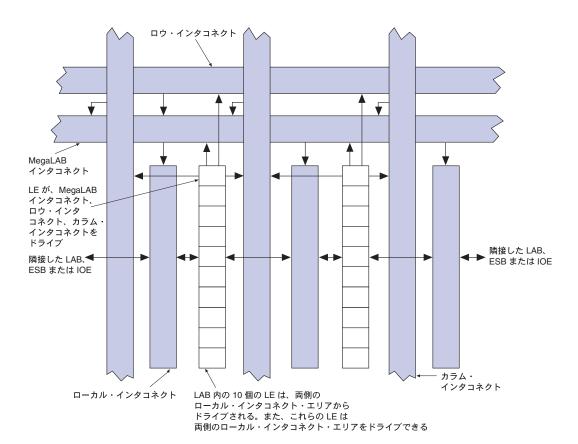

各 LAB は 10 個の LE、関連するキャリーとカスケードのチェイン、LAB コントロール信号、ローカル・インタコネクトによって構成されています。ローカル・インタコネクトは、同じ LAB または隣接した LAB 内の LE、IOE、ESB との間で信号を転送します。Quartus II のコンパイラは関連するロジックを1つの LAB または隣接した LAB 内に配置し、高速のローカル・インタコネクトを使用して高い性能を達成します。図3 は APEX 20K の LAB を示したものです。

APEX 20K デバイスには、インタリーブド LAB 構造が採用されています。この構造では、各 LE が隣接した両方向のローカル・インタコネクト領域をドライブできるようになっています。この構造の実現により、MegaLAB インタコネクトと FastTrack インタコネクトの使用が最小限に抑えられるため、さらに高い性能と柔軟性が提供されます。各 LE は高速のローカル・インタコネクトを通じて他の29個の LE をドライブできるようになっています。

### 図3. LABの構造

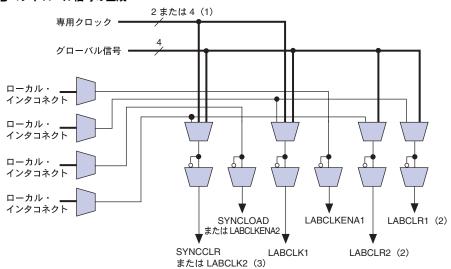

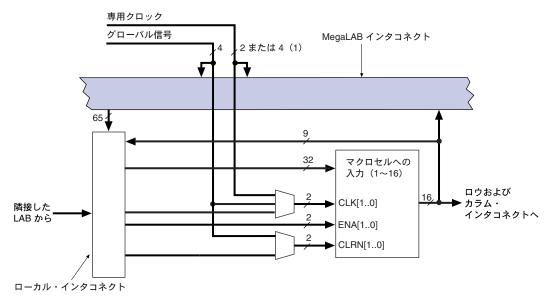

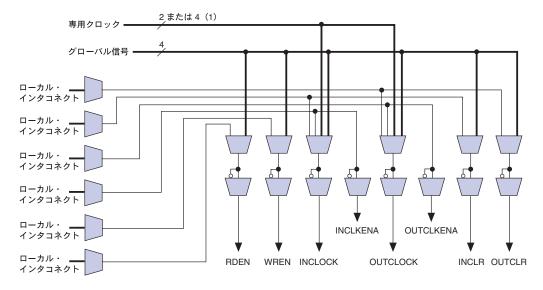

各LABには、各LEおよびESBに対するコントロール信号をドライブするための専用ロジックが内蔵されています。これらのコントロール信号には、クロック、クロック・イネーブル、非同期クリア、非同期プリセット、非同期ロード、同期クリア、同期ロードの各信号が含まれます。この場合、最大6本までのコントロール信号を同時に使用することが可能です。同期ロードおよび同期クリア信号はカウンタを構成するときに標準的に使用されますが、これらの信号は他のファンクションにも使用することができます。

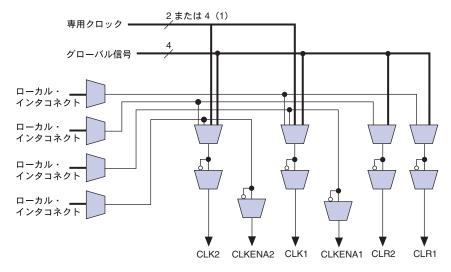

各LABでは、2本のクロックと2本のクロック・イネーブル信号を使用することができます。各LABでは、それぞれのクロック信号とクロック・イネーブル信号がリンクして使用されます(ある LAB内の LE が CLK1 を使用している場合は、この LE に CLKENA1 が使用される)。このため、同じクロック信号と異なるクロック・イネーブル信号を使用している LE がある場合は、1つの LAB内で双方のクロック信号が使用される形になるか、あるいはこれらの LE が別の LAB に配置されます。

クロックの立ち上がりと立ち下がりの双方のエッジが1つのLAB内で使用される場合も、LAB全体をカバーする双方のクロック信号が使用されることになります。

LAB全体をカバーするコントロール信号は、LABローカル・インタコネクト、グローバル信号、クロック専用ピンから生成することができます。FastTrack インタコネクトは、スキューを最小に抑えることができるため、クロックの分配にも使用されます。図4はLABコントロール信号の生成回路を示したものです。

### 図4. LABコントロール信号の生成

注:

- (1) APEX 20KEデバイスには、4本の専用クロックが提供されています。

- (2) LABCLR1とLABCLR2の信号は、LAB内のLEに対する非同期ロードと非同期プリセットもコントロールします。

- (3) SYNCCLR信号は、ローカル・インタコネクトまたはグローバル信号から生成できます。

### ロジック・エレメント

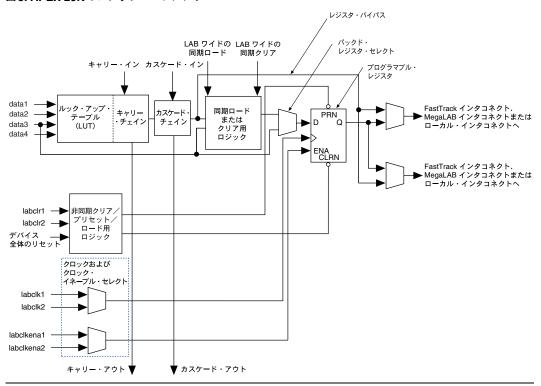

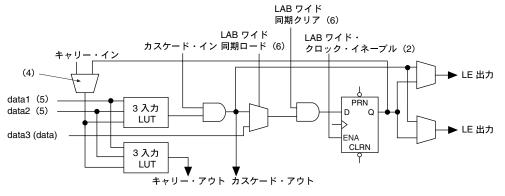

LEはAPEX 20Kアーキテクチャが提供するロジックの最小単位となっており、高いデバイス使用効率を実現するコンパクトなサイズとなっています。各LEには4変数によるあらゆる論理演算を高速で実行できる4入力のLUTが1個含まれています。さらに、各LEにはプログラマブルなレジスタが1個と、キャリー・チェイン、カスケード・チェインが組み込まれています。各LEは、ローカル・インタコネクト、MegaLABインタコネクト、およびFastTrackインタコネクトの各配線領域をドライブするようになっています。図5を参照してください。

### 図5. APEX 20Kのロジック・エレメント

各 LE 内のプログラマブル・レジスタは、D、T、JK、または SR タイプの動作を行うようにコンフィギュレーションすることができます。レジスタのクロックとクリア・コントロール信号は、グローバル信号、汎用の I/Oピン、または任意の内部ロジックからドライブすることができます。組み合わせ回路が構成される場合はレジスタがバイパスされ、LUTの出力が LE の出力を直接ドライブします。

各LEはローカル・インタコネクト、MegaLABインタコネクトまたはFastTrack インタコネクトの配線領域をドライブする2本の出力を持っています。この2本のLEの出力をLUTからの出力にするか、レジスタからの出力にするかは、それぞれ個別にコントロールすることができます。例えば、LUTが一方の出力をドライブしているときに、レジスタがもう一方の出力をドライブするような構造に設定することができます。この機能はレジスタ・パッキングと呼ばれ、LUTとレジスタをそれぞれ独立した機能に使用できるため、LEの使用効率を改善することができます。また、LUTからの出力をレジスタ付きとレジスタなしの双方でLEから出力させることもできます。

APEX 20K のアーキテクチャには、2種類の専用高速データ・パスが提供されています。1つはローカル・インタコネクトを使用しないで隣接したLE間を接続するパスで、もう一方はキャリー・チェインとカスケード・チェインです。キャリー・チェインはカウンタやアダーなどの高速演算機能を構成するときに使用され、カスケード・チェインは恒等回路 (equality comparator) のような多入力の論理機能を最小の遅延時間で実現するときに使用されます。カスケード・チェインとキャリー・チェインはLAB内のLE1からLE10を、また同じMegaLAB内のすべてのLAB間を接続することができます。

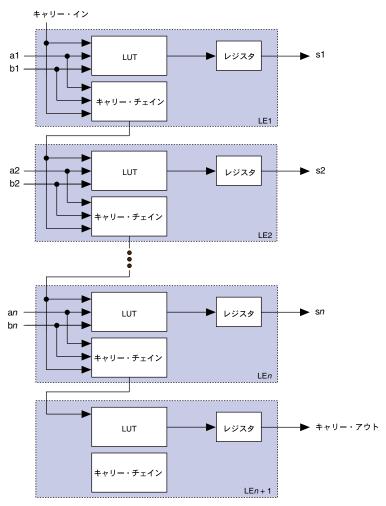

### キャリー・チェイン

キャリー・チェインはキャリーを LE 間で非常に高速で転送します。下位ビットからのキャリー・イン信号はキャリー・チェインを通って上位ビットに転送され、上位ビットのキャリー・チェインと LUT の双方に入力されます。この機能を使用することによって、APEX 20K アーキテクチャにはカウンタやアダー、指定したビット幅のコンパレータを高速で実現することができます。キャリー・チェインのロジックはデザインを処理する段階で Quartus II ソフトウェアのコンパイラによって自動的に生成され、またデザインの入力時にマニュアルで指定することもできます。LPM (Library of Parameterized Modules) や DesignWare のようなパラメータ化されたファンクションは、このキャリー・チェインの利点を自動的に活用して実現されます。

Quartus IIソフトウェアのコンパイラは、複数のLABをリンクさせることによって、10 個を超える LE で接続される長いキャリー・チェインを自動的に生成します。フィッティング機能を強化するため、長いキャリー・チェインは MegaLAB 内の LABを1 個おきにスキップするようになっています。このため、複数の LAB を通る長いキャリー・チェインは、偶数番号のLABから次の偶数番号のLABへ、あるいは奇数番号のLABから次の奇数番号のLABへと1 個のLABをスキップして接続されます。例えば、左上方に位置する MegaLAB 内の最初のLAB にある最後の LE は、この MegaLAB 内の3番目に位置する LAB の最初の LE にカスケード信号を転送するようになっています。

図6はn+1個のLEとキャリー・チェインを使ったnビットのフル・アダーがどのように実現されるかを示したものです。ここで、LUTの一部を使用して入力信号とキャリー・イン信号から2ビットのサム(和)を生成します。そして、このサムは LE の出力に接続されます。単純なアダーを構成する場合はレジスタをバイパスさせることができ、アキュムレータの機能を構成するときにレジスタを使用することもできます。LUTの他の部分とキャリー・チェインのロジックはキャリー・アウトの信号を生成し、この信号は次の上位ビットのキャリー・インに直接、接続されます。最後のキャリー・アウト信号は LE に接続され、この最後のLEからローカル・インタコネクト、MegaLABインタコネクトまたは FastTrack インタコネクトの配線領域へ出力されます。

### 図6. APEX 20Kのキャリー・チェイン

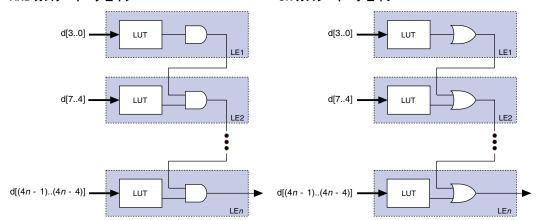

### カスケード・チェイン

APEX 20Kのアーキテクチャは、カスケード・チェインを使用して非常に大きなファン・インを持った回路機能を実現することができます。隣接している複数のLUTをパラレルに動作させ、その間の中間値をカスケード・チェインを使ってシリアルに転送させることによって、論理機能の一部を実現することができます。このカスケード・チェインは隣接したLEの出力を接続して論理積(Logical AND)またはドモルガンの反転定理による論理和(Logical OR)を実現することができます。追加される各 LE は要求される回路機能の入力ビット幅を最小の遅延時間で4ビットずつ効率的に拡張します。カスケード・チェインのロジックはデザインを処理する段階でQuartus II ソフトウェアのコンパイラによって自動的に生成され、またデザインの入力時にマニュアルで指定することもできます。

複数のLABをリンクさせることによって、10個のLEを超える長さのカスケード・チェインが自動的に生成されます。フィッティング機能を強化するため、長いカスケード・チェインは MegaLAB 内の隣のLABをスキップして接続されます。複数のLABを通る長いカスケード・チェインは、偶数番号のLABから次の偶数番号のLABへ、あるいは奇数番号のLABから次の奇数番号のLABへと1個のLABをスキップして接続されます。例えば、左上方に位置するMegaLAB内の最初のLABにある最後のLEは、このMegaLAB内の3番目に位置するLABの最初のLEにカスケード信号を転送するようになっています。図7は大きなファン・インを持つ回路機能を実現するときに、カスケード・チェインが隣接したLE間でどのように接続されるかを示したものです。

### 図7. APEX 20Kのカスケード・チェイン

### AND カスケード・チェイン

### OR カスケード・チェイン

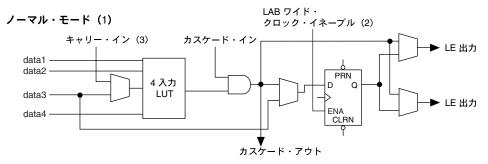

### LEの動作モード

APEX 20KのLEは次の3種類のモードのいずれかで動作します。

- ノーマル・モード

- 演算モード

- カウンタ・モード

これらの各モードでは、LEのリソースがそれぞれ異なる形で使用されます。LEには各モードで計7本の入力が提供されており(LABローカル・インタコネクトからの4本のデータ入力、プログラマブル・レジスタからのフィードバック、前段のLEからのキャリー・インとカスケード・インの計7本)、要求される論理機能を実現するためにこれらの入力はそれぞれ異なるリソースに接続されます。LAB全体をカバーするコントロール信号として、各レジスタに対するクロック、非同期クリア、非同期プリセット、非同期ロード、同期クリア、同期ロード、クロック・イネーブル・コントロールが提供されます。これらのLABワイドのコントロール信号は、すべてのLEの動作モードで使用できます。

Quartus II ソフトウェアは、LPM や DesignWare ファンクションのようなパラメータ化されたファンクションを使用して、カウンタやアダー、マルチプライヤなどのような標準的なファンクションに対して適切な動作モードを自動的に選択します。また、必要に応じて、ユーザが性能の最適化が実現されるLEの動作モードを選択して、特定用途のファンクションを作成することもできます。図8はLEの各動作モードを示したものです。

### 図8. APEX 20KのLEの動作モード

### カウンタ・モード

### 注:

- (1) ノーマル・モードのLEは、レジスタ・パッキングの機能をサポートします。

- (2) 各LABごとにLAB全体をカバーするクロック・イネーブル信号が2本提供されます。

- (3) ノーマル・モードでキャリー・インが使用された場合は、レジスタ・パッキングの機能を使用することはできません。

- (4) 各LABのLE1にはレジスタ・フィードバック・マルチプレクサが提供されます。

- (5) DATA1 と DATA2 の入力には、カウンタ・イネーブル、アップまたはダウン・コントロール信号、LAB 内の2番目以外のLEに対するレジスタ・フィードバック信号を供給することができます。

- (6) LABワイド同期クリアとLABワイド同期ロードの機能は、LAB内のすべてのレジスタに適用されます。

### ノーマル・モード

ノーマル・モードは汎用のロジック・アプリケーションや組み合わせの回路ファンクション、カスケード・チェインの長所が活用できる多入力のデコーダなどに適しています。ノーマル・モードでは、LABローカル・インタコネクトからの4本のデータ入力とキャリー・インが4入力LUTの入力になります。Quartus IIソフトウェアのコンパイラはDATA3とキャリー・インのいずれかをLUTの入力として自動的に選択します。LUTの出力をカスケード・インの信号と組み合わせることによって、カスケード・アウトの信号を持つカスケード・チェインを構成することができます。ノーマル・モードのLEは、パックド・レジスタをサポートします。

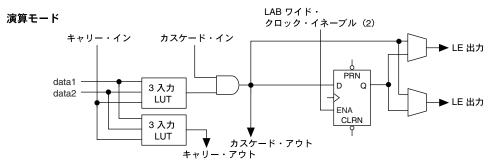

### 演算モード

演算モードは、アダー、アキュムレータ、コンパレータの構成に最適です。演算モードのLEには、2個の3入力LUTが使用されます。このうち1個のLUTは3ビットの論理関数を実現し、もう1個のLUTがキャリー・アウトを生成します。図8に示されているように、最初のLUTはキャリー・インとLABローカル・インタコネクトからの2本の入力を使用して組み合わせ出力またはレジスタ出力の論理を生成します。アダーを構成した場合は、この出力がDATA1とDATA2、およびキャリー・イン信号による3ビットのサム(和)となります。そして、2番目のLUTは同じ3本の信号からキャリー・アウト信号を生成して、キャリー・チェインを構成します。演算モードではカスケード・チェインの使用が同時にサポートされます。演算モードになっているLEは、LUTからの出力をレジスタ付きとレジスタなしの双方でLEから出力することができます。

演算モードの使用が適切と判断されるファンクションには、Quartus II ソフトウェアが自動的に演算モードを使用してパラメータ化されたファンクションを実現するため、設計者がキャリー・チェインの使用方法を指定する必要はありません。

### カウンタ・モード

カウンタ・モードには、クロック・イネーブル、カウンタ・イネーブル、同期アップ/ダウン・コントロールの各信号と、同期クリアと同期ロードのオプション信号が提供されます。カウンタ・イネーブルと同期アップ/ダウン・コントロール信号はLABローカル・インタコネクトのデータ入力から生成されます。同期クリアと同期ロードのオプション信号はLAB全体をカバーしており、LAB内のすべてのレジスタに影響を与えます。このため、LAB内のあるLEがカウンタ・モードを使用している場合は、そのLAB内の他のLEも同じカウンタの一部として使用されるか、組み合わせ回路に使用される必要があります。Quartus IIソフトウェアは、カウンタに使用されていないレジスタを他のLABへ自動的に配置します。

カウンタ・モードでは、3入力 LUT が2個使用されます。そのうちの1個はカウンタのデータを生成し、もう一方の LUT が高速のキャリー・ビットを生成します。2対1のマルチプレクサによりデータの同期ロード機能が提供され、さらに AND ゲートによる同期クリア機能もサポートされています。カウンタ・モードの LE がカスケード機能を使用している場合は、同期クリアまたは同期ロードがカスケード・チェインを転送される信号よりも優先されます。また、同期クリアが、同期ロードよりも優先して実行されるようになっています。演算モードになっている LE は、LUT からの出力をレジスタ付きとレジスタなしの双方で LE から出力することができます。

### クリアおよびプリセット・ロジックのコントロール

レジスタのクリアとプリセットの信号に対するロジックは、LAB全体をカバーする信号でコントロールされます。LEは非同期クリアの機能を直接サポートしています。Quartus IIソフトウェアのコンパイラは、Not-gate push-backを使用したテクニックにより非同期プリセットとエミュレーションを実現することもできます。さらに、Quartus IIソフトウェアのコンパイラはこのプログラマブルな Not-gate push-backを使用したテクニックにより、プリセットとクリアまたは非同期ロードと同時にエミュレーションを実現することもできます。ただし、このテクニックには、レジスタあたり3個のLEがさらに必要となります。このようなエミュレーション機能は、デザインがコンパイルされるときに自動的に実現されます。プリセットとロードの機能を同時にエミュレートするようになっているレジスタは、チップ・ワイドのリセット信号がアサートされたとき、または電源投入後に、不定のステートに入ります。

2種類のクリアおよびプリセット・モードに加え、APEX 20K デバイスにはデバイス内すべてのレジスタをリセットするチップ・ワイドのリセット・ピン (DEV\_CLRn) が提供されています。このピンの使用は、Quartus II ソフトウェアでコンパイル前に設定できます。チップ・ワイドのリセット信号は他のすべてのコントロール信号よりも優先されます。非同期のプリセットを使用しているレジスタは、チップ・ワイドのリセット信号がアサートされたときに、プリセットされます。これは、非同期プリセットの機能が極性反転のテクニックを使用して実現されているためです。

### FastTrackインタコネクト

APEX 20K のアーキテクチャには、LE、ESB、および I/O ピン間の接続を行う FastTrack インタコネクトが提供されています。この FastTrack インタコネクトはデバイス全体を垂直および水平方向に走っている連続した配線チャネルとなっています。このグローバルな配線構造により、複雑なデザインにおいてもその性能が予測可能となっています。これに対して、配線領域が分割されている FPGAでは、一定しない複数のパスを接続するためのスイッチ・マトリックスが必要となり、ロジック・リソース間のディレイが大きくなって性能が低下します。

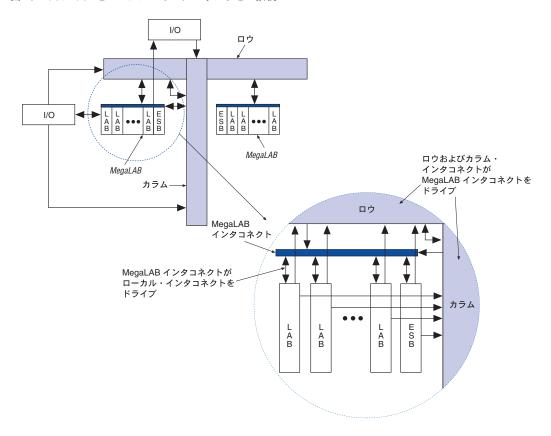

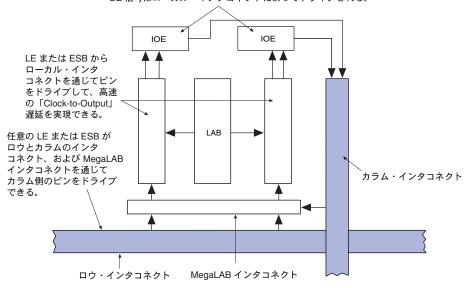

FastTrack インタコネクトは、デバイス全体をカバーしているロウとカラムのインタコネクト・チャネルによって構成されています。ロウ・インタコネクトは同じロウに位置する MegaLAB間の信号を接続し、カラム・インタコネクトは同じカラムの MegaLAB間の信号を接続します。ロウおよびカラム・インタコネクトを使用することにより、LE、IOE、または ESB からデバイス内の任意の LE、IOE、または ESB をドライブすることができます。図9を参照してください。

### 図9. APEX 20Kの配線構造

ロウ・ラインは、同じロウに位置する LE、IOE、または ESB からダイレクトにドライブすることができます。 さらに、カラム・ラインはロウ・ラインをドライブすることができるため、LE、IOE または ESB からカラム・インタコネクトとロウ・インタコネクトを通じて異なるロウに位置する各エレメントをドライブすることができます。ロウ・インタコネクトが特定の MegaLAB内にある LE、IOE または ESB をドライブするときは、MegaLABインタコネクトを通じてドライブします。

カラム・ラインは、同じカラムに位置するLE、IOE、またはESBからダイレクトにドライブすることができます。デバイス内の左端と右端に位置するカラム・ラインは、ロウIOEからもドライブできます。カラム・ラインはあるロウ・ラインから別のロウ・ラインに信号を接続するときにも使用されます。カラム・ラインはロウ・ラインをドライブすることができ、MegaLABインタコネクトもダイレクトにドライブできるようになっているため、ロウ間の高速配線が実現されます。

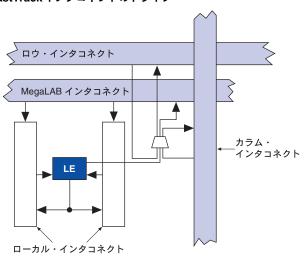

図 10は、FastTrackインタコネクトがMegaLAB内のLEをドライブするときに、ローカル・インタコネクトがどのように使用されるかを示したものです。

### 図 10. FastTrack とローカル・インタコネクトとの接続

図11はロウ・インタコネクトとカラム・インタコネクトが交差する領域を示したもので、各配線リソースとLEがどのように接続されるかが示されています。

### 図11. FastTrack インタコネクトのドライブ

APEX 20KE デバイスには、大きなファン・アウトを持つ入力信号をより高速で 配線することができる特別な配線構造が採用されています。APEX 20KE デバイ スのカラムI/Oピンは、信号をMegaLABインタコネクトを経由せずにローカル・ インタコネクトをダイレクトにドライブすることができる FastRow インタコネ クトと接続できます。FastRow インタコネクトは、2個の MegaLAB をドライブ します。これらのピンはローカル・インタコネクトをダイレクトにドライブでき るため、高速のセットアップ・タイムが実現されます。EP20K300Eおよびそれよ り集積度の高いデバイスでは、FastRowインタコネクトは左上の2個のMegaLAB と右下の2個のMegaLABをドライブします。EP20K200Eおよびそれより集積度 の低いデバイスでは、FastRow インタコネクトはデバイスの上段にある2個の MegaLAB と、デバイスの下段にある2個の MegaLAB をドライブします。すべ てのデバイスで、FastRow インタコネクトは該当する MegaLAB のすべてのロー カル・インタコネクトをドライブします。ただし、MegaLAB の左端と右端のイ ンタコネクト領域は除きます。FastRow インタコネクトに直接接続する Pin を使 用することで、信号が MegaLab インタコネクト・ラインを経由しないでディス ティネーションの LE に到達するため、高速なセットアップ・タイムが実現され ます。図12は、FastRowインタコネクトの構造を示したものです。

### 図12. APEX 20KEの FastRow インタコネクト

表9は、APEX 20K アーキテクチャの各エレメントが他のエレメントとどのように接続できるかをまとめたものです。

| 表 9. APEX 2                 | 表 9. APEX 20K デバイス内での配線方法 |                  |          |          |                      |                        |   |                                 |                        |

|-----------------------------|---------------------------|------------------|----------|----------|----------------------|------------------------|---|---------------------------------|------------------------|

| ソース                         |                           |                  |          |          | ディステ                 | ィネーション                 | / |                                 |                        |

|                             | ロウ<br>I/O<br>ピン           | カラム<br>I/O<br>ピン | LE       | ESB      | ローカル・<br>インタ<br>コネクト | MegaLAB<br>インタ<br>コネクト |   | カラム<br>FastTrack<br>インタ<br>コネクト | FastRow<br>インタ<br>コネクト |

| ロウI/Oピン                     |                           |                  |          |          | ✓                    | ✓                      | ✓ | ✓                               |                        |

| カラム<br>I/O ピン               |                           |                  |          |          | <b>√</b> (1)         |                        |   | <                               | <b>√</b> (1)           |

| LE                          |                           |                  |          |          | ✓                    | ✓                      | ✓ | ✓                               |                        |

| ESB                         |                           |                  |          |          | ✓                    | ✓                      | ✓ | ✓                               |                        |

| ローカル・<br>インタコネクト            | <b>\</b>                  | <b>\</b>         | <b>✓</b> | <b>✓</b> |                      |                        |   |                                 |                        |

| MegaLAB<br>インタコネクト          |                           |                  |          |          | <b>✓</b>             |                        |   |                                 |                        |

| ロウ FastTrack<br>インタコネクト     |                           |                  |          |          |                      | <b>✓</b>               |   | <b>✓</b>                        |                        |

| カラム<br>FastTrack<br>インタコネクト |                           |                  |          |          |                      | ~                      | ~ |                                 |                        |

| FastRow<br>インタコネクト          |                           |                  |          |          | <b>√</b> (1)         |                        |   |                                 |                        |

### 注:

(1) この接続はAPEX 20KEデバイスでのみサポートされます。

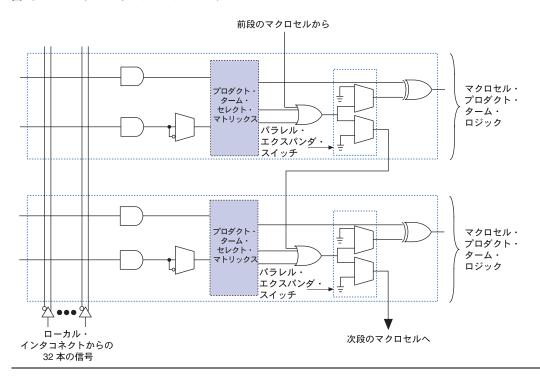

### プロダクト・ターム・ロジック

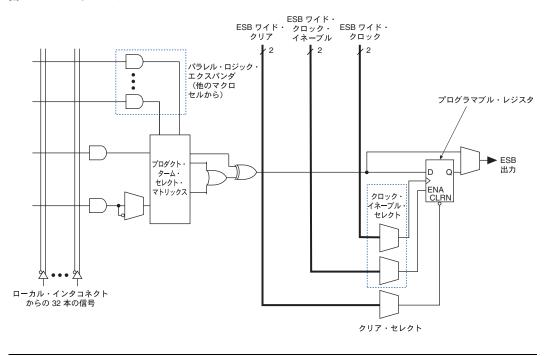

MultiCore アーキテクチャのプロダクト・タームは、ESBによって実現されます。ESB はマクロセルのブロックとして動作するようにコンフィギュレーションすることができ、この設定は各 ESB ごとに個別に行うことができます。各 ESB には隣接するローカル・インタコネクトから 32 本の入力信号が与えられるようになっているため、MegaLAB インタコネクトまたは隣接した LAB からも ESB をドライブすることができます。また、ESB のマクロセルから 9 本の出力信号がローカル・インタコネクトを通じてフィードバックされるようになっており、高い性能を実現することができます。クロック専用ピン、グローバル信号、ローカル・インタコネクトからの追加入力は、ESB のコントロール信号をドライブすることができます。

プロダクト・ターム・モードでは、各 ESB に 16 個のマクロセルが構成されます。各マクロセルは、2本のプロダクト・タームと1 個のプログラマブル・レジスタで構成されます。図 13はプロダクト・ターム・モードの ESB を示したものです。

### 図13. プロダクト・ターム・モードのときの ESB

### 注:

(1) APEX 20KEデバイスには、4本の専用クロックが提供されています。

### マクロセル

APEX 20Kのマクロセルは、シーケンシャル回路または組み合わせ回路の動作を行うように個別にコンフィギュレーションすることができます。マクロセルは、ロジック・アレイ、プロダクト・ターム・セレクト・マトリックス、そしてプログラマブル・レジスタの3つのファンクショナル・ブロックで構成されています。

組み合わせ回路のロジックは、プロダクト・タームで実現されます。プロダクト・ターム・セレクト・マトリックスは、組み合わせ回路を実現するときにプロダクト・タームを OR ゲートまたは XOR ゲートへの入力にするか、他のマクロセルのロジック・リソースを増加させるためのパラレル・エクスパンダとして使用するかを選択します。 1 本のプロダクト・タームには極性反転の機能が提供されており、Quartus II ソフトウェアはこの機能を使用してドモルガンの極性反転を実行し、多入力の OR ファンクションをより効率的に実現します。 Quartus II ソフトウェアのコンパイラは、Not-gate push-back を使用したテクニックにより非同期プリセットとエミュレーションを実現します。図 14 は APEX 20K のマクロセル構造を示したものです。

### 図14. APEX 20K のマクロセル

レジスタ付きのファンクションを実現するときは、各マクロセルのレジスタをプログラマブルなクロック・コントロール付きのD、T、JK、SR g4 g7 g8 の動作を行うように個別にプログラムすることができます。組み合わせ回路の動作を行わせるときは、このレジスタをパイパスすることができます。デザインの入力時に、ユーザが要求されるレジスタのタイプを指定することができ、g8 Quartus g9 下の大力を引きないでは、g9 できるとができ、g9 を対してリソースの使用効率が最適化される最も効率的なレジスタの動作を選択させることもできます。g9 の動作を選択させることもできます。g9 に最も効率的となるレジスタ動作を自動的に選択します。

各プログラマブル・レジスタには、ESB全体をカバーする2本のクロックのうちのいずれか1本を使用することができます。このESBワイド・クロックは、デバイスのクロック専用ピン、グローバル信号、またはローカル・インタコネクトから供給できます。また、各クロックには、これと関連するローカル・インタコネクトから供給される1本のクロック・イネーブル信号が提供されます。クロックとクロック・イネーブル信号は特定のESB内でセットで使用されるようになっており、マクロセルであるクロック信号が使用されている場合は、このクロックと関連しているクロック・イネーブルが使用されます。

クロックの立ち上がりと立ち下がりの双方のエッジが1つのESB内で使用される場合も、ESB全体をカバーする双方のクロック信号が使用されることになります。

プログラマブル・レジスタは、非同期クリアの機能もサポートします。ESB内では、グローバル信号とローカル・インタコネクトから、計2本の非同期クリア信号が提供されます。各マクロセルでは、これら2本の非同期クリア信号のいずれか1本を選択することができ、クリア機能のない構造に設定することもできます。また、ESBでは、2本のクリア信号のいずれか1本を極性反転させて使用することもできます。図15は、ESBにプロダクト・タームを構成したときに提供されるコントロール・ロジックを示したものです。

### 図 15. プロダクト・ターム・モードの ESB に提供されるコントロール・ロジック

### 注:

(1) APEX 20KEデバイスには、4本の専用クロックが提供されています。

### パラレル・エクスパンダ

パラレル・エクスパンダは、高速で複雑なロジック・ファンクションを実現する場合に、各マクロセルで未使用のプロダクト・タームを隣接したマクロセルに分配できるようにしたものです。パラレル・エクスパンダを使用することによって、ESB内の隣接したマクロセルからの30本のパラレル・エクスパンダと、そのマクロセルが持つ2本の計32本のプロダクト・タームをORロジックにダイレクトに入力することができます。

Quartus  $\Pi$ ソフトウェアのコンパイラは2本までのパラレル・エクスパンダを1セットとして、最大15セットまでをマクロセルに自動的に割り当てることができます。この2本のパラレル・エクスパンダが使用されるごとに、小さな追加タイミング遅延が発生します。図 16 は APEX 20K のパラレル・エクスパンダを示したものです。

### 図 16. APEX 20K のパラレル・エクスパンダ

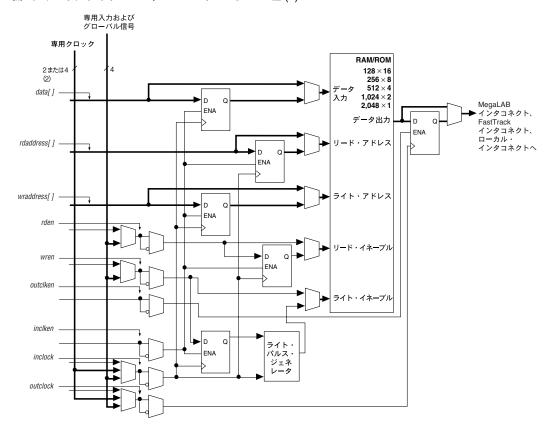

# エンベデッド・ システム・ ブロック

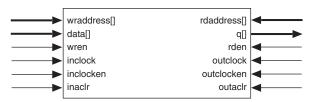

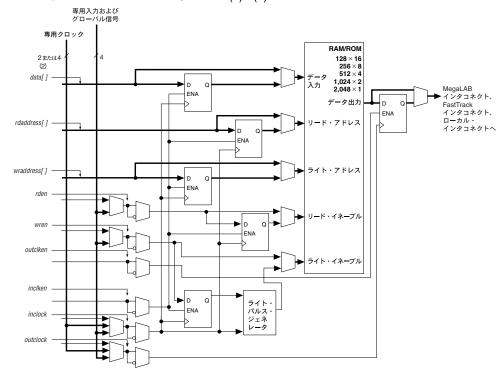

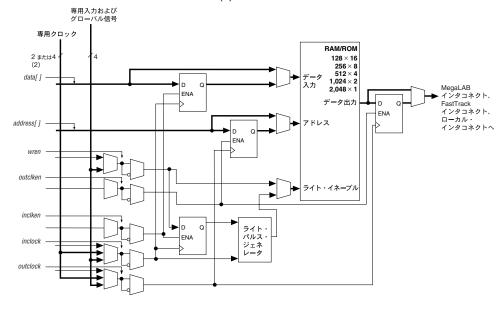

ESBには、デュアル・ポートRAM、ROM、FIFO、CAMを含む多様なメモリ・ブロックを構成することができます。ESBには入力レジスタと出力レジスタが含まれています。入力レジスタはライト動作に同期し、出力レジスタはシステム性能の改善を実現するデザインのパイプライン化が可能になっています。ESBは、リードとライトの動作を異なるクロック周波数で同時に実行できるデュアル・ポート・モードをサポートしています。図17はESBの信号を示したブロック図です。

### 図17. ESBのブロック図

ESBには同期型のRAMも実現することができ、同期型のRAMは非同期型のRAMよりも簡単に構成することができます。非同期型のRAMを使用する回路ではライト・イネーブル(WE)信号を生成する必要があり、アドレスとデータの信号はこのWEに対して規定されたセットアップ・タイムとホールド・タイムの規格を守る必要があります。これに対してESBを使用した同期型RAMでは自分自身のWE信号が生成され、対応するグローバル・クロックに対してタイミングが取られます。セルフ・タイミング機能を持つESBのRAMでは、コントロールが必要となるタイミングは、グローバル・クロックに対して規定されるセットアップ・タイムとホールド・タイムのみとなります。

ESB の入力は隣接するローカル・インタコネクトからドライブすることができ、このローカル・インタコネクトは MegaLABインタコネクトまたは FastTrack インタコネクトからドライブできるようになっています。 ESB はローカル・インタコネクトからドライブできるようになっているため、隣接する LE から ESB をダイレクトにドライブして、高速のアクセスを実現することができます。 ESB の出力は MegaLAB インタコネクトと FastTrack インタコネクトをドライブします。また、ESB の 10 本の出力のうち 9 本は独立した出力ラインとなっており、これらの出力は、隣接する LE との高速配線やプロダクト・ターム・モードにおける高速フィードバックを実現するときにローカル・インタコネクトをドライブします。

ESBにメモリを実現する場合は、各 ESBのメモリ構成を  $128 \times 16$ .  $256 \times 8$ .  $512 \times 4$   $1,024 \times 2$ . または  $2,048 \times 1$  のいずれかに任意に設定することができます。また、Quartus II ソフトウェアは複数の ESB を接続して、さらに大容量のメモリを自動的に実現します。例えば、  $128 \times 16$  構成の RAM を 2 個接続して  $128 \times 32$  の RAM ブロックを実現することができ、 $512 \times 4$  構成の RAM を 2 個接続して  $512 \times 8$  の RAM ブロックを実現することができます。 ESB のメモリ性能は、 2,048 ワードの深さまで低下することがありません。各 ESB には 2,048 ワードの深さのメモリを構成することができるため、各 ESB をパラレルに動作させることによって、外部にコントロール・ロジック回路を設ける必要性がなくなり、これらの回路による遅延時間を発生することもありません。

2,048 ワードを超える深さの高速 RAM ブロックを構成する場合は、ESB の出力からトライ・ステート・ラインをドライブするようにします。そして、各トライ・ステート・ラインを同じカラムに配置されている MegaLAB 内のすべての ESB と接続し、カラム FastTrack を通じて MegaLAB インタコネクトとロウとカラムの FastTrack をドライブするようにします。各 ESB はプログラマブル・デコーダを使用して対応するトライ・ステート・ドライバがアクティブになるようにします。例えば、8,192 ワードの深さのメモリを構成するときは、4個の ESB が使用されます。この場合は、11 本のアドレス・ラインが ESB メモリをドライブし、さらに2本がトライ・ステート・デコーダをドライブします。どの位置の 2,048 ワード分のメモリ・ページに相当するかに応じて、該当する ESB のドライバがオンとなり、出力がトライ・ステート・ラインへドライブされます。 Quartus II ソフトウェアは、このような深いサイズのメモリを構成するとき、複数の ESB をトライ・ステート・ライン付きで自動的に接続します。内部のトライ・ステートをコントロールするロジックは、内部信号の競合やフローティング・ラインが発生しないように設計される必要があります。図 18 を参照してください。

# アドレス・デコーダ ESB システム・ロジックへ ESB

### 図18. 複数のESBを接続して深いメモリを構成する方法

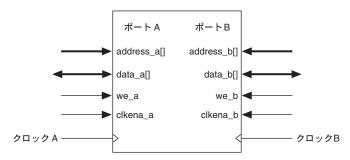

ESBには、リード/ライト・クロック・モードと、入力/出力クロック・モードの2種類のデュアル・ポート・メモリを実現することができます。また、ESBを使用して、2つのポートを使用してリードとライトの動作を同時に実行できる双方向のデュアル・ポート・メモリを構成することができます。このような種類のデュアル・ポート・メモリを実現するには、同時に行われる2つのリードまたはライトをサポートするために、ESBを2個または4個使用します。図19はこの機能を示したものです。

### 図19. デュアル・ポート RAM を実現したときの APEX 20Kの ESB

### リード/ライト・クロック・モード

リード/ライト・クロック・モードには、2本のクロックが使用されます。このうち1本のクロックは、ライト動作に関係するすべてのレジスタをコントロールし、データ入力、WE、ライト・アドレスの各レジスタに供給されます。もう1本のクロックはリード動作に関係するすべてのレジスタをコントロールし、リード・イネーブル(RE)、リード・アドレス、データ出力の各レジスタに供給されます。ESBはクロック・イネーブルと非同期クリアもサポートしており、これらの信号はリード・レジスタとライト・レジスタを個別にコントロールすることができます。リード/ライト・クロック・モードは、リードとライトの動作が異なるシステム周波数で発生するアプリケーションに対して共通に使用されます。図 20 はリード/ライト・クロック・モードになっている ESB を示したものです。

### 図20. リード/ライト・クロック・モードの ESB 注 (1)

注:

- (1) ESBローカル・インタコネクト信号、グローバル信号、またはチップ全体のリセットによって、すべてのレジスタを非同期でクリアすることができます。

- (2) APEX 20KEデバイスには、4本の専用クロックが提供されています。

### 入力/出力クロック・モード

入力/出力クロック・モードにも2本のクロックが使用されます。1本のクロックはESBにデータを入力するためのすべてのレジスタをコントロールし、データ入力、WE、RE、リード・アドレス、ライト・アドレスの各レジスタに供給されます。もう1本のクロックはESBのデータ出力レジスタをコントロールします。このとき、ESBはクロック・イネーブルと非同期クリアもサポートしており、これらの信号はリード・レジスタとライト・レジスタを個別にコントロールすることができます。入力/出力クロック・モードは、リードとライトの動作が同じ周波数で発生するアプリケーションに共通に使用できますが、入力と出力のレジスタには異なるクロック・イネーブル信号が必要となります。図21は入力/出力クロック・モードになっているESBを示したものです。

### 図 21. 入力/出力クロック・モードの ESB 注 (1)、(2)

### 注:

- (1) ESBローカル・インタコネクト信号、グローバル信号、またはチップ全体のリセットによって、すべてのレジスタを非同期でクリアすることができます。

- (2) APEX 20KEデバイスには、4本の専用クロックが提供されています。

### シングル・ポート・モード

APEX 20KのESBは、リードとライトの動作を同時に行う必要がないときに使用されるシングル・ポートのモードもサポートしています。図22を参照してください。

### 図 22. シングル・ポート・モードの ESB 注 (1)

### 注:

- (1) ESBローカル・インタコネクト信号、グローバル信号、またはチップ全体のリセットによって、すべてのレジスタを非同期でクリアすることができます。

- (2) APEX 20KEデバイスには、4本の専用クロックが提供されています。

## **CAM (Content-Addressable Memory)**

APEX 20KE デバイスでは、ESB に CAM を実現することができます。CAM は RAM と反対の動作を行うと考えることができます。RAM は、リード動作において、与えられたアドレスに対するデータを出力します。CAM はこれと反対に、与えられたデータに対するアドレスを出力します。例えば、FA12 のデータがアドレス 14 にストアされている場合は、FA12 のデータが入力されると、14 が出力されます。

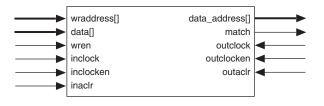

CAMは高速サーチの動作に使用されます。RAMブロック内のデータをサーチする場合、サーチ動作がシリアルに実行されます。このため、特定のデータ・ワードを発見するためには、多くのサイクル数が必要となります。CAMはすべてのアドレスをパラレルにサーチして、特定のワードをストアしているアドレスを出力します。一致したアドレスが発見された場合には、「match」のフラグがHighにセットされます。図23はCAMの信号を示したブロック図です。

### 図 23. APEX 20KE に実現される CAM のブロック図

CAM はネットワーキング、コミュニケーション、データ圧縮、キャッシュ・マネージメントなどの高速サーチ動作が要求されるアプリケーションに使用できます。

APEX 20KE のオン・チップ CAM は、従来からあるディスクリート・タイプの CAM デバイスよりも高い性能を実現します。CAM とロジックを APEX 20KE デバイス内に集積化することによって、オン・チップおよびオフ・チップの遅延時間が解消されるため、システム性能が改善されます。

CAMのモードでは、各 ESB に 32 ワード× 32 ビットの CAM が構成されます。複数の CAM を接続し、LE に補助的なロジックを実現することによって、さらに深い CAM やデータ幅の広い CAM を構成することができます。 Quartus II ソフトウェアは複数の ESB と LE を接続して、さらに大容量の CAM を自動的に実現します。

CAM はメモリのワードに対する「ドント・ケア」ビットの書き込みをサポートしています。「ドント・ケア」ビットは、CAM の比較をマスキングするときに使用でき、「ドント・ケア」に設定されたビットがマッチングの動作に影響を与えることはありません。

CAM の出力はエンコードされたフォーマット、またはエンコードなしのいずれかに設定できます。出力がエンコードされるときは、ESBがデータの位置をエンコードされたアドレスとして出力します。例えば、データがアドレス 12 にストアされているときは、ESBが 12 を出力します。エンコードされない出力の場合は、ESBが 16 本の出力を使用してデータの位置を 2 クロック・サイクルで示します。この場合、データがアドレス 12 にストアされているときには、12 番目の出力がHigh になります。エンコードなしの出力が使用される場合は、16 ビット出力のバスを使用して 32 ワードの状態を示すため、出力の読み出しには 2 クロック・サイクルが必要になります。

エンコードされた出力は、CAM に重複したデータが書き込まれないデザインに適しています。重複したデータが2個所に書き込まれると、CAM の出力は正しくなりません。CAM に重複したデータが書き込まれる可能性がある場合は、エンコードされない出力を使用するのが適当です。エンコードされていない出力を使用したCAMでは、複数のデータの位置を識別することができます。

CAM にはデータをコンフィギュレーション時にプリロードすることができ、システムの動作時にデータを書き込むこともできます。ほとんどの場合、CAM の各ワードへの書き込みには2クロック・サイクルが必要です。「ドント・ケア」のビットを使用するときは、3番目のクロック・サイクルが必要になります。

APEX 20KEデバイスとCAM については、アプリケーション・ノート、AN 119 「Implementing High-Speed Search Applications with APEX CAM」を参照してください。

### ESB に対する信号のドライブ

ESBに対するコントロール信号のドライブには、柔軟性に富んだオプションが用意されています。まず、ESBの入力と出力には、異なるクロックが使用できます。データ入力、データ出力、リード・アドレス、ライト・アドレス、WE信号、RE信号には、それぞれ個別のレジスタを挿入することができます。また、グローバル信号とローカル・インタコネクトからの信号は、WEとREもドライブすることができます。グローバル信号、クロック専用ピンとローカル・インタコネクトからも ESB のクロックをドライブすることができます。LE からローカル・インタコネクトをドライブすることができるため、LEでWEとRE、ESBクロック、クロック・イネーブル、非同期のクリアの各信号をコントロールすることも可能です。図24は ESB コントロール信号を生成するロジックを示したものです。

#### 図24. ESB コントロール信号の生成回路

#### 注:

(1) APEX 20KEデバイスには、4本の専用クロックが提供されています。

ESB に対する入力は、隣接する LE からドライブされるローカル・インタコネクトを通じて (ESBへの高速接続パス)、または MegaLABインタコネクトから与えることができます。 ESB の出力は、ローカル・インタコネクト、 MegaLABインタコネクト、または FastTrack インタコネクトの配線領域を通じて、同じ MegaLAB内の LE、IOE、およびデバイス内の任意の LE と IOE をドライブすることができます。

### ROMにロジックを実現する方法

ESBにはプロダクト・タームによるロジックだけでなく、コンフィギュレーション時に ESB へリード・オンリのパターンをプログラムして1つの大きな LUT を構成することによって、ロジックの機能を実現することもできます。LUT を使用した組み合わせ回路では、ロジックの出力が論理演算ではなくこの LUT にプログラムされたパターンによって決定されます。この方法によって実現される組み合わせ回路は通常のロジックを実現するアルゴリズムを使用した場合よりも高速となり、この高い性能は ESB の提供する高速アクセス・タイムによってさらに強化されています。また、ESB の高い集積度により、複数の LE や分散型の RAM ブロックを結合させた場合の配線遅延を発生させることなく、複雑なロジック・ファンクションを1段のロジック・レベルで実現することができます。LPM のようなパラメータ化されたファンクションは、ESB の利点を自動的に活用することができます。また、Quartus II ソフトウェアは、ESB の使用が適切となるデザイン部分をESB で実現できるようになっています。

## プログラマブルなスピード/パワー・コントロール

APEX 20Kの ESB には、非常に高速な動作を各 ESB ごとにサポートする高速モードが提供されています。この高速モードの動作を必要としない場合は、この機能をオフにして、ESB の消費電力を 50% まで低減することができます。 ESB をロー・パワー・モードで動作させた場合には、一定の追加タイミング遅延が発生します。この動作モードの設定を行う Turbo Bit TM のオプションは、プロダクト・ターム・モードまたはメモリ・ファンクションが実現されている ESB に提供されます。使用されていない ESB はパワー・ダウン状態となり、DC 電流を消費することはありません。

APEX 20K デバイス内の各 ESB には、高速モードまたはロー・パワー・モードのいずれかをプログラムすることができます。このため、デザイン内でスピードがクリティカルとなる部分を高速モードで動作させ、残りのパスを低速で動作させて消費電力を低減させることができます。

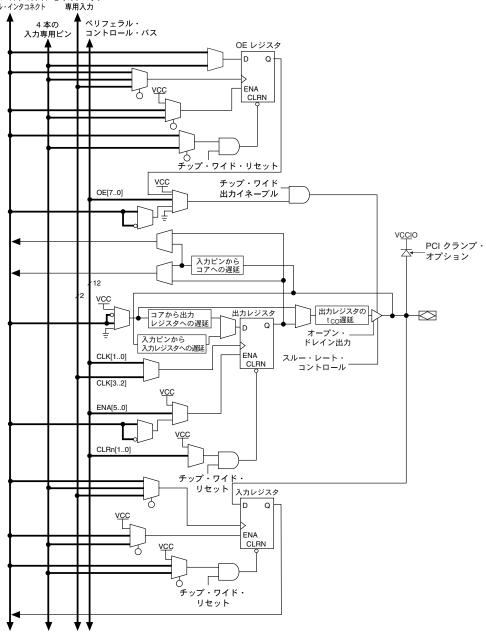

## 1/0 の構造

APEX 20KのI/Oエレメント(IOE)には、双方向のI/Oバッファとレジスタが各1個内蔵されています。このレジスタは、高速のセットアップ・タイムを必要とする外部データに対する入力レジスタとして、あるいは高速の「Clock-to-Output」遅延を必要とするデータに対する出力レジスタとして使用することができます。IOE は入力ピン、出力ピン、または双方向ピンとして使用することができます。高速な双方向I/Oタイミングを実現するために、ローカル配線を使用するLEレジスタはセットアップ・タイムとOEタイミングを改善できます。Quartus II ソフトウェアのコンパイラはプログラマブルな極性反転オプションを使用して、ロウまたはカラム・インタコネクトからの信号の極性を反転させます。APEX 20KのIOEでは、各ピンごとに1本の出力イネーブル信号が提供されるため、Quartus II ソフトウェアのコンパイラは効率的にオープン・ドレインの動作を実現させることができます。

APEX 20Kの IOE には、0 nsのホールド・タイムや最小の「Clock-to-Output」時間を確保し、入力 IOE レジスタからコア・レジスタへの転送またはコア・レジスタから出力 IOE レジスタへの転送を最小限にするためのプログラマブルな遅延コントロール機能が内蔵されています。レジスタをダイレクトにドライブしているピンのパスに0 nsのホールド・タイムを確保するための遅延が必要になったり、組み合わせ回路のロジックを通じてレジスタをドライブしているピンのパスに遅延が不要になることがあります。

表 10は、APEX 20K のプログラマブルな遅延と Quartus II ソフトウェアのロジック・オプションを示したものです。

| 表 10. APEX 20K のプログラマブルな遅延チェイン |                       |  |  |  |

|--------------------------------|-----------------------|--|--|--|

| プログラマブルな遅延                     | Quartus IIのロジック・オプション |  |  |  |

| 入力ピンからコアまでの遅延                  | 内部セルへの入力遅延を低減する       |  |  |  |

| 入力ピンから入力レジスタまでの遅延              | 入力レジスタへの入力遅延を低減する     |  |  |  |

| コアから出力レジスタまでの遅延                | 出力レジスタへの入力遅延を低減する     |  |  |  |

| 出力レジスタ t <sub>CO</sub> の遅延     | 出力ピンへの遅延を増やす          |  |  |  |

Quartus II ソフトウェアのコンパイラは、これらの遅延コントロール機能を自動的に設定して0 ns のホールド・タイムを確保しながら最小のセットアップ・タイムが実現されるようにします。図 25 は、APEX 20K デバイスに双方向の高速 I/Oがどのように実現されるかを示したものです。

APEX 20KのIOEに内蔵されているレジスタには、コンフィギュレーションの完了時に「パワー・アップ High」(初期値が High)または「パワー・アップ Low」(初期値が Low)のいずれかを設定することができます。レジスタを「パワー・アップ Low」に設定した場合は、非同期クリア信号でレジスタをコントロールすることができます。また、「パワー・アップ High」に設定された場合は、レジスタを非同期でクリアしたり、プリセットすることができなくなります。この機能は、APEX 20K デバイスがアクティブ Low の入力信号または他のデバイスをコントロールしている場合に便利です。この機能を利用することによって、電源投入直後に意図しない入力がアクティブになることを防止できます。

## 図 25. APEX 20K の双方向 I/O レジスタ 注 (1)

ロウおよびカラム・インタコネクト、2本のクロック またはローカル・インタコネクト 専用入力

注:

(1) 出力イネーブルと入力レジスタは双方向ピンに隣接しているLAB内のLEレジスタです。

APEX 20KE デバイスには、FastRow インタコネクトをドライブする強化された IOE が実現されています。FastRow インタコネクトは、カラム I/Oピンと2つの MegaLAB内の LAB ローカル・インタコネクトをダイレクトに接続します。この機能は、PCI のデザインのような複雑なロジックの大きなファン・アウトを持つピンに対して、高速のセットアップ・タイムを実現します。高速な双方向 I/Oタイミングを実現するために、ローカル配線を使用する LE レジスタはセットアップ・タイムと OE タイミングを改善できます。APEX 20KE の IOE はオープン・ドレインの信号をダイレクトにサポートしており、オープン・ドレイン信号に対して、より高速の「Clock-to-Output」遅延を実現します。APEX 20KEの IOE 内に内臓されているプログラマブルな遅延コントロール機能はマルチ・レベルで遅延時間をコントロールすることができ、要求されるセットアップ・タイムやホールド・タイムのファイン・チューニングを行うことができます。Quartus IIソフトウェアのコンパイラは、これらの遅延コントロール機能を自動的に設定して0 nsのホールド・タイムを確保しながら最小のセットアップ・タイムが実現されるようにします。

表 11 は、APEX 20KE のプログラマブルな遅延と Quartus II ソフトウェアのロジック・オプションを示したものです。

| 表 11. APEX 20KE のプログラマブルな遅延チェイン |                        |  |  |  |

|---------------------------------|------------------------|--|--|--|

| プログラマブルな遅延                      | Quartus II のロジック・オプション |  |  |  |

| 入力ピンからコアまでの遅延                   | 内部セルへの入力遅延を低減する        |  |  |  |

| 入力ピンから入力レジスタまでの遅延               | 入力レジスタへの入力遅延を低減する      |  |  |  |

| コアから出カレジスタまでの遅延                 | 出力レジスタへの入力遅延を低減する      |  |  |  |

| 出カレジスタ <b>t<sub>CO</sub>の遅延</b> | 出力ピンへの遅延を増やす           |  |  |  |

| クロック・イネーブル遅延                    | クロック・イネーブル遅延を増やす       |  |  |  |

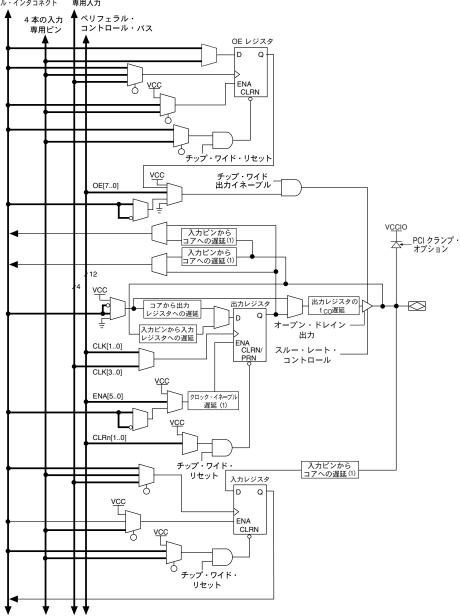

APEX 20KE の IOE に内蔵されているレジスタには、コンフィギュレーションの完了後に「パワー・アップ High」または「パワー・アップ Low」にする設定を行うことができます。レジスタを「パワー・アップ Low」に設定した場合は、非同期クリア信号でレジスタをコントロールすることができます。また、「パワー・アップ High」に設定された場合は、非同期プリセット信号でレジスタをコントロールすることができます。図 26 は、APEX 20KE デバイスに双方向の高速 I/O ピンがどのように実現されるかを示したものです。この機能は、APEX 20KE デバイスがアクティブ Low の入力信号または他のデバイスをコントロールしている場合に便利です。この機能を利用することによって、電源投入直後に意図しない入力がアクティブになることを防止できます。

## 図 26. APEX 20KE の双方向 I/O レジスタ 注 (1)、(2)

ロウおよびカラム・インタコネクト、 4本のクロック FastRow またはローカル・インタコネクト 専用入力

## 注:

- (1) このプログラマブル遅延は、オフおよび3レベルの計4段階での設定を行うことができます。

- (2) 出力イネーブルと入力レジスタは双方向ピンに隣接しているLAB内のLEレジスタです。

各IOEを入力または双方向のピンとして使用した場合は、各IOEからロウとカラムのインタコネクト、MegaLABまたはローカル・インタコネクトをドライブします。ロウ側のIOEはローカル・インタコネクト、MegaLABインタコネクト、ロウとカラムのインタコネクトをドライブすることができ、カラム側のIOEはカラム・インタコネクトをドライブできます。図27はロウ側のIOEが各インタコネクトとどのように接続されるかを示したものです。

#### 図27. ロウ側のIOEと各インタコネクトとの接続

図 28は、カラム IOE が各インタコネクトとどのように接続されるかを示したものです。

#### 図28. カラム側のIOE と各インタコネクトとの接続

各 IOE からカラム・インタコネクトをドライブできる。 APEX 20KE デバイスでは、IOE が FastRow インタコネクトと カラム・インタコネクトもドライブできる。各 IOE のデータと OE 信号はローカル・インタコネクトによってドライブされる。

## 専用高速I/Oピン

APEX 20KE デバイスには、PCI コントロール信号のような大きい内部ファンアウトを持つ双方向ピンをサポートするための拡張機能が組み込まれています。このようなピンは専用高速I/Oピン(FAST1、FAST2、FAST3、および FAST4)と呼ばれ、専用入力に置き替わります。これらのピンは高速クロック、クリア、または大きなファンアウト・ロジック信号の分配に使用できます。ドライブ・アウトもできます。専用高速I/Oピンのデータ出力とトライ・ステート・コントロールは、高速動作用の隣接するMegaLABからローカル・インタコネクトがドライブします。

### 最新標準I/O規格のサポート

APEX 20KEのIOEは、LVTTL、LVCMOS、1.8 VのI/O、2.5 VのI/O、3.3 VのPCI、PCI-X、3.3 VのAGP、LVDS、LVPECL、GTL+、CTT、HSTLのClass I、SSTL-3のClass IおよびII、SSTL-2のClass IとIIをサポートしています。

APEX 20KE デバイスがサポートしている標準 I/O 規格の詳細については、アプリケーション・ノート、AN 117 「Using Selectable I/O Standards in Altera Devices」を参照してください。

APEX 20KE デバイスには8個のI/Oバンクが内蔵されています。OFPパッケー ジでは、バンクをリンクした4個のI/Oバンクが形成されています。I/Oバンク は LVDS と LVPECL を除くすべての標準 I/O 規格を直接サポートします。すべ ての I/O バンクは外部抵抗を追加することで LVDS と LVPECL をサポートでき ます。さらに、バンク内の1つのブロックに高速な True-LVDS 入力と LVPECL 入力をサポートする回路があり、特定のバンク内の別のブロックは、高速な True-LVDS 出力と LVPECL 出力をサポートします。LVDS ブロックはすべての標準 I/O 規格をサポートします。各 I/O バンクには専用の VCCIO ピンがあります。 各バンクごとに異なる標準規格を個別にサポートすることができるため、1つの デバイスで1.8 V、2.5 V、および3.3 Vのインタフェースをサポートすることがで きます。各バンクには、別個の $V_{REF}$ レベルを使用できるため、バンクごとに任 意のターミネーション付き標準規格 (SSTL-3など) をサポートすることができま す。1つのバンク内では、終端された標準のうちどれでも1つをサポートすること ができます。EP20K300E およびこれよりも高集積の APEX 20KE デバイスは、 LVDSインタフェースのデータ・ピンをサポートしています(EP20K300Eより集 積度の低いデバイスでは、LVDSのクロック・ピンがサポートされますが、デー タ・ピンはサポートされません)。EP20K300E およびこれよりも高集積のデバイ スはすべて、チャネルあたり最大155 MBのデータ・ピンを実現するLVDSイン タフェースをサポートします。オーダー・コードの末尾に "X" のサフィックス が付く EP20K400E およびこれよりも高集積のデバイスには、高速サポートのた めのシリアライザ/デシリアライザ回路とPLLが追加されています。

各バンクは、出力ピンの VCCIO が同じである複数の規格をサポートすることができます。各バンクはリファレンス電圧を使用する1つの標準I/O規格をサポートしますが、VCCIO 電圧レベルが同じであれば複数の標準I/O 規格をサポートできます。例えば、VCCIOが3.3 Vである場合、1つのバンクでLVTTL、LVCMOS、3.3 VのPCI、およびSSTL-3の入力と出力をサポートできます。

LVDS対応バンクがLVDS I/Oバンクとして使用されない場合、LVDS対応バンクが他のすべての標準I/O規格をサポートします。図 29は APEX 20KEの I/Oバンクの配置を示しています。

#### I/O バンク 1 I/O バンク 2 I/O バンク 3 通常のI/O ブロックがサポートする規格 LVTTL 1/0 バンク8 (1) **LVCMOS** 2.5 V LVDS/LVPECL 1.8 V 入力ブロック 3.3 V PCI (2) LVPECL HSTL Class I LVDS/LVPECL GTL+ 出力ブロック SSTL-2 Class I and II (2) SSTL-3 Class I and II I/O バンク 4 CTT (1) AGP I/O バンク7 個々の・ 電源バス I/O バンク 6 I/O バンク 5

#### 図29. APEX 20KEのI/Oバンク

注:

- (1) LVDS ブロックに隣接する最初の2つのI/Oピンは、 $V_{CCIO}$ プレーンの適切なノイズ・レベルを維持するための入力としてのみ使用できます。

- (2) LVDSの入力ブロックと出力ブロックがLVDSに使用されない場合、これらのブロック は他のすべての標準I/O規格をサポートし、 $V_{\rm CCIO}$ を3.3 V、2.5 V、または1.8 Vに設定した入力ピン、出力ピン、または双方向ピンとして使用できます。

## 電源のシーケンスと活線挿抜

APEX 20K デバイスは複数の電源電圧がある環境で使用されることがあるため、可能性のある電源の投入シーケンスに対応できるように設計されています。したがって、 $V_{CCIO}$ と $V_{CCINT}$ の電源は任意の順番で投入することができます。

電源投入前および投入時に、デバイスにダメージを与えることなく、信号をAPEX 20K デバイスに入力することができます。また、APEX 20K デバイスは、電源の投入時に出力をドライブしません。デバイスが規定された動作条件に達し、コンフィギュレーションが完了すると、APEX 20K デバイスはユーザが規定した動作を行います。

# MultiVolt I/O インタフェース

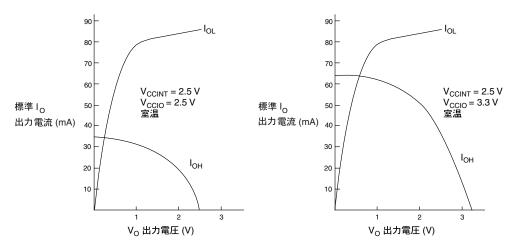

APEX デバイスのアーキテクチャは MultiVolt I/O インタフェース機能をサポートしており、すべてのパッケージの APEX デバイスは異なる電源電圧を使用しているシステムとインタフェースすることができます。これらのデバイスは内部のロジック動作と入力バッファ用の VCC ピン(VCCINT)と、I/O ピンの出力ドライバ用の VCC ピン(VCCIO)の2種類の電源ピンを持っています。

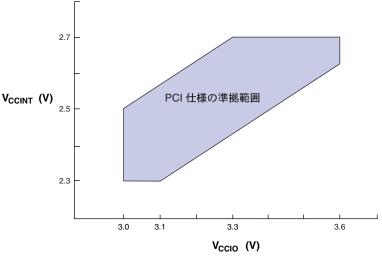

APEX 20Kの VCCINTピンは、常に 2.5 V の電源に接続されている必要があります。 2.5 V の  $V_{CCINT}$  レベルでは、入力ピンは 2.5 V および 3.3 V を許容します。オーダー・コードでスピード・グレードの後に "V"のサフィックスが付くデバイス(EP20K400BC652-1V など)は 5.0 V を許容します。VCCIOピンは要求される出力のレベルに応じて、2.5 V または 3.3 V の電源に接続することができます。VCCIOピンを 2.5 V の電源に接続した場合、出力レベルは 2.5 V のシステムと互換性を持つようになります。VCCIOピンを 3.3 V の電源に接続した場合、出力の High レベルが 3.3 V となり、3.3V または 5.0 V のシステムと互換性を持つようになります。

表 12 は 5.0 V を許容する APEX 20K デバイスの MultiVolt I/O サポートをまとめたものです。

| 表 12. 5.0         | 表 12. 5.0 V を許容する APEX 20K デバイスの MultiVolt I/O サポート |              |                  |              |     |     |

|-------------------|-----------------------------------------------------|--------------|------------------|--------------|-----|-----|

| V <sub>CCIO</sub> | 入力信号 (V) 出力信号 (V)                                   |              |                  |              |     | ')  |

| (V)               | 2.5                                                 | 2.5 3.3 5.0  |                  |              | 3.3 | 5.0 |

| 2.5               | ✓                                                   | <b>√</b> (1) | <b>√</b> (1) (2) | ✓            |     |     |

| 3.3               | ✓                                                   | ✓            | <b>√</b> (1) (2) | <b>√</b> (3) | ✓   | ✓   |

#### 注:

- (1)  $V_{\text{CCIO}}$  よりも高い電圧を持つ入力をドライブするには、PCI クランプ・ダイオードを ディセーブルする必要があります。

- (2) "V"のサフィックスが付いたAPEX 20Kデバイスは5.0 Vを許容します。

- (3)  $V_{\text{CCIO}} = 3.3 \text{ V}$  である場合、APEX 20K デバイスは 3.3 V を許容する入力を持つ 2.5 V デバイスをドライブできます。

$5.0\,\mathrm{V}$  の電源に対するプルアップ抵抗が接続された、 $5.0\,\mathrm{V}$  を許容する APEX 20K デバイスのオープン・ドレイン出力ピンは、 $3.5\,\mathrm{V}$  の  $\mathrm{V}_{\mathrm{IH}}$  を必要とする  $5.0\,\mathrm{V}$  の CMOS 入力ピンをドライブすることができます。また、ピンがインアクティブの 場合は、この配線パターンは抵抗を介して  $5.0\,\mathrm{V}$  にプルアップされます。オープン・ドレインのピンはトライ・ステートまたは  $\mathrm{Low}\,\mathrm{V}$  ベルのいずれかをドライブ し、 $\mathrm{High}\,\mathrm{V}$  ベルをドライブすることはありません。この立ち上がり時間はプルアップ抵抗と負荷インピーダンスの値に依存します。プルアップ抵抗を設定する 場合は、 $\mathrm{IoI}$  の規格を考慮する必要があります。

APEX 20KE デバイスも MultiVolt I/O インタフェース機能をサポートしています。APEX 20KE VCCINT ピンは、常に 1.8 V の電源に接続されている必要があります。1.8 V の  $V_{\text{CCINT}}$  レベルでは、入力ピンは 1.8 V、2.5 V、および 3.3 Vを許容します。VCCIO ピンは標準 I/O 規格に要求されるレベルに応じて、1.8 V、2.5 V、または 3.3 V の電源に接続することができます。VCCIO ピンを 1.8 V の電源に接続した場合、出力レベルは 1.8 V のシステムと互換性を持つようになります。VCCIO ピンを 2.5 V の電源に接続した場合、出力レベルは 2.5 V の 2.5

表13はAPEX 20KEのMultiVolt I/Oサポートをまとめたものです。

| 表 13. APE         | EX 20KEのI         | MultiVolt I/C | )サポート        |              |     |              |     |     |

|-------------------|-------------------|---------------|--------------|--------------|-----|--------------|-----|-----|

| V <sub>CCIO</sub> | AD信号 (V) 出力信号 (V) |               |              |              |     |              |     |     |

| (V)               | 1.8               | 2.5           | 3.3          | 5.0          | 1.8 | 2.5          | 3.3 | 5.0 |

| 1.8               | ✓                 | <b>√</b> (1)  | <b>√</b> (1) |              | ✓   |              |     |     |

| 2.5               |                   | ✓             | <b>√</b> (1) |              |     | ✓            |     |     |

| 3.3               |                   | ✓             | ✓            | <b>√</b> (2) |     | <b>√</b> (2) | ✓   | ✓   |

#### 注:

- (1) 5.0 V 入力の場合を除いて、 $\text{V}_{\text{CCIO}}$  よりも高い電圧を持つ入力をドライブするには、PCI クランプ・ダイオードをディセーブルする必要があります。

- (2) APEX 20KE デバイスは外部抵抗を追加することで 5.0 V を許容できるようになります。

- (3)  $V_{CCIO}$ が3.3 V である場合、APEX 20KE デバイスは3.3 V を許容する入力を持つ2.5 V デバイスをドライブできます。

# ClockLock と ClockBoost の機能

APEX 20Kデバイスは、PLLを使用して実現されているClockLockとClockBoost の機能をサポートしています。ClockLockは、クロック信号をPLL回路に同期させ、デバイス内に分配されるクロックの遅延とスキューを低減します。この低減により、0 ns のホールド・タイムを維持しながら、セットアップ・タイムと「Clock-to-Output」遅延を最小に抑えることができます。ClockBoost はクロック周波数の逓倍機能を実現するもので、この機能を使用してデバイス内のリソースの共有化を実現し、エリア効率を改善することができます。また、ClockBoost回路を利用することによって、ボード上に低速のクロックを分配し、デバイス内部でこれを逓倍して使用することができます。APEX 20K デバイスには、ASICとは異なる高速のクロック・ツリーが内蔵されており、ユーザがクロック・ツリーを設計したり、最適化する必要はありません。APEX 20Kデバイスの高速クロックを実現する ClockLock と ClockBoost の機能は、システム性能と帯域幅の大幅な改善を実現します。オーダー・コードで"X"のサフィックスが付くデバイスには ClockLock 回路が内蔵されています。

APEX 20Kデバイスの ClockLock と ClockBoostの機能は、Quartus II ソフトウェアによって設定されます。これらの機能の使用に外部デバイスは必要ありません。

逓倍されたクロックと逓倍されないクロックの双方が必要となるデザインにおいても、ボード上のクロックの配線パターンを CLK2p のピンに接続することができます。表14は ClockLock と ClockBoost 回路でサポートされるクロック周波数の逓倍比の組み合わせを示したものです。 CLK2p ピンからの入力は APEX 20K デバイスの ClockLock と ClockBoost の双方と接続できます。 ただし、双方の回路が使用された場合は、もう一方のクロック・ピン(CLK1p)を使用することはできません。

| 表 14. 逓倍比の組み合わせ |         |  |

|-----------------|---------|--|

| Clock 1         | Clock 2 |  |

| ×1              | ×1      |  |

| × 1、×2          | × 2     |  |

| × 1、 × 2、 × 4   | × 4     |  |

#### APEX 20KEのClockLock機能

APEX 20KE デバイスには、さらに強力な ClockLock 機能が内蔵されています。これらのデバイスには最大 4 個までの PLL 回路が提供されており、それぞれの PLL 回路を独立に使用することができます。このうち 2 個は、汎用 PLL 回路または LVDS インタフェースのいずれかに使用できる(LVDS の I/O ピンをサポートしているデバイスの場合)ように設計されています。残りの 2 個は、汎用の PLL 回路として設計されています。EP20K200E およびこれより集積度の低いデバイスには 2 個の PLL 回路が内蔵されており、EP20K300E およびこれより集積度の高いデバイスには 4 個の PLL 回路が内蔵されています。

以下のセクションでは、APEX 20KE デバイスの PLL 回路によって提供される機能を解説します。

### PLLの外部フィードバック

ClockLock回路の出力信号をチップの外部に出力し、システム内にある他のデバイスのクロック・ピンをドライブすることができます。さらに、PLLのフィードバック・ループをデバイスの外部に接続することもできます。この機能を使用することによって、APEX 20KE デバイスと SDRAM のような他の高速デバイス間のI/Oインタフェースを精密にコントロールすることが可能になります。

## クロックの逓倍機能

APEX 20KE デバイスの ClockBoost 回路は、クロック周波数の逓倍と分周をプログラマブルな数値で行うことができます。この場合、出力の周波数は、入力のクロック周波数に  $m/(n\times k)$  を乗算した値となります。ここで、m および k は 2 から 160 までの値であり、n は 1 から 16 までの値です。クロック周波数の逓倍および分周機能を使用することによって、時分割動作(Time-domain Multiplexing)のファンクションなどを実現し、デザインに使用される LE の数を減少させることができます。

#### クロックの位相と遅延の調整

APEX 20KEデバイスに提供されているClockShift機能を使用することによって、クロックの位相と遅延の調整が可能になります。クロックの位相は90度単位で調整可能です。1クロック周期までのクロック遅延を任意の範囲で増加または減少させることができます。

#### LVDSのサポート

2個の PLL は、LVDS インタフェースをサポートするために設計されています。 LVDS が使用される場合は、I/O クロックがデータ転送レートよりも低速のレートで動作します。このため、PLLを使用してI/O クロックの周波数を内部で逓倍し、LVDSのデータ・レートに対応させることになります。例えば、840 メガビット/秒(Mbps)のデータ・レートとなっている LVDS をサポートするときは、I/O クロックを 105 MHz で動作させることができます。この場合、PLL はこの高速データ・レートをサポートするために入力クロックを 8 逓倍します。 EP20K400E およびそれより高集積のデバイスでは、PLLを使用して高速な LVDS インタフェースをサポートできます。

### Lock 信号

APEX 20KEの ClockLock 回路では、それぞれ独立した LOCK 信号がサポートされています。 ClockLock 回路が入力クロックにロックしているとき、LOCK 信号は High レベルをドライブします。 LOCK 信号は各 ClockLock 回路ごとにオプションとして使用することができ、これらが使用されていない場合は、I/Oピンとなります。

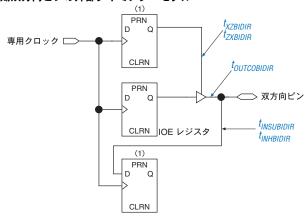

### ClockLock と ClockBoost のタイミング・パラメータ

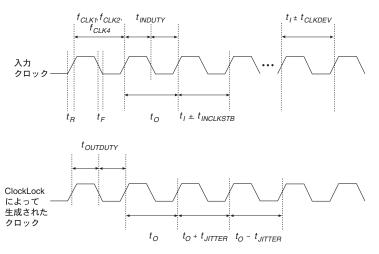

ClockLock および ClockBoost の回路を適切に動作させるためには、入力される クロックが一定の要求を満たしている必要があります。入力クロックが要求される規格に適合していない場合には、これらの回路が入力クロックにロックせず、デバイス内で不適切なクロックが生成される可能性があります。ClockLock と ClockBoost の回路によって生成されるクロックも一定の規格を満足しなければ なりません。入力クロックがコンフィギュレーション時に要求される規格に適合していれば、APEX 20Kの ClockLock と ClockBoost の回路はコンフィギュレーション時に入力クロックとロックします。そして、コンフィギュレーション完了後すぐに、これらの回路が使用可能となります。APEX 20KE デバイスではクロック入力規格はプログラマブルであるため、デバイスがコンフィギュレーションされるまで PLL はクロックに応答できません。PLL はコンフィギュレーション完了後すぐに入力クロックにロックします。図 30 は入力クロックと生成クロックの規格に適用されるタイミング・パラメータを示したものです。

ClockLockとClockBoostの回路の詳細については、アプリケーション・ ノート、AN 115 「Using the ClockLock and ClockBoost PLL Features in APEX Devices」(日本語版有り)を参照してください。

## 図30. 入力クロックと生成クロックに適用されるタイミング・パラメータ

$t_1$ パラメータは通常の入力クロック周期、 $t_0$ パラメータは通常の出力クロック周期として参照されます。

表 15 は -1 スピード・グレードの APEX 20K デバイスに対する ClockLock と ClockBoost 回路のタイミング・パラメータをまとめたものです。

| シンボル                  | パラメータ                                                                   | 最小 | 最大            | 単位  |

|-----------------------|-------------------------------------------------------------------------|----|---------------|-----|

| f <sub>OUT</sub>      | 出力周波数                                                                   | 25 | 180           | MHz |

| f <sub>CLK1</sub> (1) | 入力クロック周波数(ClockBoostの逓<br>倍比が1のとき)                                      | 25 | 180<br>(1)    | MHz |

| f <sub>CLK2</sub>     | 入力クロック周波数(ClockBoostの逓<br>倍比が2のとき)                                      | 16 | 90            | MHz |

| f <sub>CLK4</sub>     | 入力クロック周波数(ClockBoostの逓<br>倍比が4のとき)                                      | 10 | 48            | MHz |

| t <sub>OUTDUTY</sub>  | ClockLock/ClockBoost による生成ク<br>ロックのデューティ・サイクル                           | 40 | 60            | %   |

| f <sub>CLKDEV</sub>   | Quartus II ソフトウェアで規定された入<br>カクロック周波数からの許容誤差<br>(ClockBoostの逓倍比が1のとき)(2) |    | 25,000<br>(3) | PPM |

| t <sub>R</sub>        | 入力クロック立ち上がり時間                                                           |    | 5             | ns  |

| t <sub>F</sub>        | 入力クロック立ち下がり時間                                                           |    | 5             | ns  |

| t <sub>LOCK</sub>     | ClockLock/ClockBoostがロックするまでに必要な時間 (4)                                  |    | 10            | μs  |

| 表 15. – 1 スピード・グレードの APEX 20K デバイスに対する ClockLock と |

|----------------------------------------------------|

| ClockBoost 回路のタイミング・パラメータ (2/2)                    |

| シンボル                  | パラメータ                                           | 最小 | 最大  | 単位 |

|-----------------------|-------------------------------------------------|----|-----|----|

| t <sub>SKEW</sub>     | 関連する ClockLock/ClockBoost による<br>生成クロック間のスキュー遅延 |    | 500 | ps |

| t <sub>JITTER</sub>   | ClockLock/ClockBoost による生成ク<br>ロックのジッタ (5)      |    | 200 | ps |

| t <sub>INCLKSTB</sub> | 入力クロックの安定度(隣接したク<br>ロック間で測定)                    |    | 50  | ps |

#### 注:

- (1) 通倍比が1のとき、EP20K100-1XのPLL入力周波数の範囲は25 MHzから175 MHzま

- (2) 入力クロックのすべての規格に適合している必要があります。クロックの規格に適合し ていない場合には、PLLが入力クロックにロックせず、デバイス内で不適切なクロック が生成される場合があります。

- (3) デバイスのコンフィギュレーション時にはClockLockとClockBoostの回路が最初にコ ンフィギュレーションされます。コンフィギュレーション時に入力クロックが供給され た場合は、ロックの時間がデバイス全体のコンフィギュレーションに要する時間よりも 短いため、コンフィギュレーションの実行中に ClockLock と ClockBoost の回路が入力 クロックにロックします。

- (4)  $t_{JITTER}$ の規格は、長時間にわたる観測で測定されています。 (5) 入力クロックの安定度が100 psの場合、 $t_{JITTER}$ は250 psです。

表 16 は -2 スピード・グレードの APEX 20K デバイスに対する ClockLock と ClockBoost 回路のタイミング・パラメータをまとめたものです。

|                       | ?スピード・グレードの APEX 20K ラ<br>ockBoost 回路のタイミング・パラメ                        |     | する Cloc       | kLock と |

|-----------------------|------------------------------------------------------------------------|-----|---------------|---------|

| シンボル                  | パラメータ                                                                  | 最小  | 最大            | 単位      |

| f <sub>OUT</sub>      | 出力周波数                                                                  | 25  | 170           | MHz     |

| f <sub>CLK1</sub>     | 入力クロック周波数(ClockBoost の逓倍比が1のとき)                                        | 25  | 170           | MHz     |

| f <sub>CLK2</sub>     | 入力クロック周波数(ClockBoost の逓倍比が2のとき)                                        | 16  | 80            | MHz     |

| f <sub>CLK4</sub>     | 入力クロック周波数(ClockBoost の逓倍比が4のとき)                                        | 10  | 34            | MHz     |

| t <sub>OUTDUTY</sub>  | ClockLock/ClockBoost による生成クロックのデューティ・サイクル                              | 40  | 60            | %       |

| f <sub>CLKDEV</sub>   | Quartus IIソフトウェアで規定された入<br>カクロック周波数からの許容誤差<br>(ClockBoostの逓倍比が1のとき)(1) |     | 25,000<br>(2) | PPM     |

| t <sub>R</sub>        | 入力クロック立ち上がり時間                                                          |     | 5             | ns      |

| t <sub>F</sub>        | 入力クロック立ち下がり時間                                                          |     | 5             | ns      |

| t <sub>LOCK</sub>     | ClockLock/ClockBoost がロックするまでに必要な時間 (3)                                |     | 10            | μs      |

| t <sub>SKEW</sub>     | 関連する ClockLock/ClockBoost による<br>生成クロック間のスキュー遅延                        | 500 | 500           | ps      |

| t <sub>JITTER</sub>   | ClockLock/ClockBoost による生成クロックのジッタ (4)                                 |     | 200           | ps      |

| t <sub>INCLKSTB</sub> | 入力クロックの安定度 (隣接したクロック間で測定)                                              |     | 50            | ps      |

#### 注:

- (1) Quartus II のソフトウェアを使用して ClockLock と ClockBoost の回路を実現する場合は、入力周波数を指定する必要があります。 Quartus II のソフトウェアは ClockLock と ClockBoost の PLL 回路をこの周波数にチューニングします。  $f_{CLKDEV}$  のパラメータは、デバイスの動作中における入力クロック周波数の規定された値からの変動範囲を規定しています。シミュレーションにおいて、このパラメータが反映されることはありません。

- (2) 25,000 PPM (parts per million) は入力クロック周期の2.5%に相当します。

- (3) デバイスのコンフィギュレーションの期間において、ClockLock と ClockBoost の回路 はデバイス内の他の部分よりも先にコンフィギュレーションされます。コンフィギュレーション期間に入力クロックが供給された場合は、t<sub>LOCK</sub>の値がデバイス全体のコンフィギュレーションに要する時間よりも短いため、コンフィギュレーションの期間中に ClockLock と ClockBoost の回路が入力クロックにロックします。

- (4)  $t_{IIITER}$ の規格は、長時間にわたる観測で測定されています。

表 17 および 18 は、APEX 20KE デバイスに対する ClockLock と ClockBoost 回路 のタイミング・パラメータをまとめたものです。

| シンボル                      | パラメータ                                      | 条件 | 最小 | 標準 | 最大             | 単位            |

|---------------------------|--------------------------------------------|----|----|----|----------------|---------------|

| t <sub>R</sub>            | 入力クロック立ち上がり時間                              |    |    |    | 5              | ns            |

| t <sub>F</sub>            | 入力クロック立ち下がり時間                              |    |    |    | 5              | ns            |

| t <sub>INDUTY</sub>       | 入力クロックのデューティ・サイクル                          |    | 40 |    | 60             | %             |

| t <sub>INJITTER</sub>     | ピークからピークへの入力ジッタ                            |    |    |    | 入力周期の<br>2%    | ピークから<br>ピークへ |

| t <sub>OUTJITTER</sub>    | ClockLockまたはClockBoostによる生成クロックのジッタ        |    |    |    | 出力周期の<br>0.35% | RMS           |

| t <sub>OUTDUTY</sub>      | ClockLockまたはClockBoostによる生成クロックのデューティ・サイクル |    | 45 |    | 55             | %             |

| t <sub>LOCK (2)</sub> (3) | ClockLockまたはClockBoostがロック<br>するまでに必要な時間   |    |    |    | 40             | μs            |

| シンボル                 | パラメータ                    | 標準I/O規格         | – 1Xスピード・<br>グレード |     | - 2Xスピード・<br>グレード |     | 単位  |

|----------------------|--------------------------|-----------------|-------------------|-----|-------------------|-----|-----|

|                      |                          |                 | 最小                | 最大  | 最小                | 最大  |     |

| f <sub>VCO (4)</sub> | 電圧がコントロールされた発振器の動<br>作範囲 |                 | 200               | 500 | 200               | 500 | MHz |

| f <sub>CLOCK0</sub>  | 内部で使用する Clock0 PLL 出力周波数 |                 | 1.5               | 335 | 1.5               | 200 | MHz |

| CLOCK1               | 内部で使用する Clock1 PLL 出力周波数 |                 | 20                | 335 | 20                | 200 | MHz |

| CLOCK0_EXT           | 外部の clock0 出力に使用する出力ク    | 3.3 VのLVTTL     | 1.5               | 245 | 1.5               | 226 | MHz |

|                      | ロック周波数                   | 2.5 VのLVTTL     | 1.5               | 234 | 1.5               | 221 | MHz |

|                      |                          | 1.8 VのLVTTL     | 1.5               | 223 | 1.5               | 216 | MHz |

|                      |                          | GTL+            | 1.5               | 205 | 1.5               | 193 | MHz |

|                      |                          | SSTL-2 Class I  | 1.5               | 158 | 1.5               | 157 | MHz |

|                      |                          | SSTL-2 Class II | 1.5               | 142 | 1.5               | 142 | MHz |

|                      |                          | SSTL-3 Class I  | 1.5               | 166 | 1.5               | 162 | MHz |

|                      |                          | SSTL-3 Class II | 1.5               | 149 | 1.5               | 146 | MHz |

|                      |                          | LVDS            | 1.5               | 420 | 1.5               | 350 | MHz |

| CLOCK1_EXT           | 外部の clock1 出力に使用する出力ク    | 3.3 VのLVTTL     | 20                | 245 | 20                | 226 | MHz |

| _                    | ロック周波数                   | 2.5 VのLVTTL     | 20                | 234 | 20                | 221 | MHz |

|                      |                          | 1.8 VのLVTTL     | 20                | 223 | 20                | 216 | MHz |

|                      |                          | GTL+            | 20                | 205 | 20                | 193 | MHz |

|                      |                          | SSTL-2 Class I  | 20                | 158 | 20                | 157 | MHz |

|                      |                          | SSTL-2 Class II | 20                | 142 | 20                | 142 | MHz |

|                      |                          | SSTL-3 Class I  | 20                | 166 | 20                | 162 | MHz |

|                      |                          | SSTL-3 Class II | 20                | 149 | 20                | 146 | MHz |

|                      |                          | LVDS            | 20                | 420 | 20                | 350 | MHz |

| i<br>IN              | 入力クロック周波数                | 3.3 VのLVTTL     | 1.5               | 290 | 1.5               | 257 | MHz |

|                      |                          | 2.5 VのLVTTL     | 1.5               | 281 | 1.5               | 250 | MHz |

|                      |                          | 1.8 VのLVTTL     | 1.5               | 272 | 1.5               | 243 | MHz |

|                      |                          | GTL+            | 1.5               | 303 | 1.5               | 261 | MHz |

|                      |                          | SSTL-2 Class I  | 1.5               | 291 | 1.5               | 253 | MHz |

|                      |                          | SSTL-2 Class II | 1.5               | 291 | 1.5               | 253 | MHz |

|                      |                          | SSTL-3 Class I  | 1.5               | 300 | 1.5               | 260 | MHz |

|                      |                          | SSTL-3 Class II | 1.5               | 300 | 1.5               | 260 | MHz |

|                      |                          | LVDS            | 1.5               | 420 | 1.5               | 350 | MHz |

## 注:

- (1) 入力クロックのすべての規格に適合している必要があります。クロックの規格に適合していない場合には、PLL が入力クロックにロックせず、デバイス内で不適切なクロックが生成される場合があります。

- (2) 最大ロック時間は、 $40 \, \mu s$  または  $2000 \, \lambda$  カクロック・サイクルのいずれか早い方になります。

- (3) コンフィギュレーション前の PLL 回路はディセーブルされたパワー・ダウンの状態です。コンフィギュレーション中も PLLはまだディセーブルされた状態です。PLLはデバイスがユーザ・モードになるとロックを開始します。クロック・イネーブル機能を使用している場合は、CLKLK\_ENAピンがユーザ・モードでHighになるとロックが開始します。

- (4) PLLのVCO動作範囲は、LVDSモードで200 $^{\rm m}$ Hz  $\leq$  f $_{\rm VCO}$   $\leq$  840 MHz です。

# SignalTap エンベデッド・ ロジック・ アナライザ

APEX 20K デバイスには、SignalTap と呼ばれるエンベデッド・ロジック・アナライザをサポートする機能が内蔵されています。この機能を内蔵させることによって、IEEE Std. 1149.1(JTAG)回路を通じてデバイス内部の任意のレジスタをモニタすることが可能になっています。このため、内部信号をI/Oピンに出力させることなく、内部のロジックの状態を実際のスピードで解析することができます。この機能は FineLine BGA パッケージのような最先端パッケージを使用するデザインで特に重要となります。これは、ボードのデザインと組立て後のデバッグ工程でモニタするピンに対する接続を追加することが困難になるためです。

# IEEE Std. 1149.1 (JTAG) バウンダリ・ スキャンの サポート

APEX 20K ファミリのすべてのデバイスは、IEEE Std.1149.1-1990 の標準規格に準拠した JTAG BST をサポートしています。EP20K1500E は JTAG BYPASS インストラクションのみをサポートします。JTAG バウンダリ・スキャン・テストはコンフィギュレーションの前か後で実行できますが、コンフィギュレーションの期間中には実行できません。APEX 20K デバイスの JTAG ポートは、Quartus II ソフトウェア、または Jam ファイル(.jam)や Jam バイト・コード・ファイル(.jbc)を採用したハードウェアによるコンフィギュレーションを実行するときにも使用されます。さらに、APEX 20K デバイス(EP20K1500E 以外)の JTAG ポートは、SignalTap エンベデッド・ロジック・アナライザでデバイスのロジック動作をモニタするときにも使用されます。APEX 20K デバイスは表 19 に示されている JTAG インストラクションをサポートしています。

| JTAGインストラクション            | 内容                                                                                                                                                                              |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD           | 動作中のデバイスのピンから信号を取り込んでテストすることができる。また、最初の<br>データ・パターンをデバイス・ピンに出力させることができる。これは、SignalTap エン<br>ベデッド・ロジック・アナライザによっても使用される。                                                          |

| EXTEST                   | 出カピンにテスト・パターンを強制的に与え、入力ピンのデータを取り込んでテスト結果<br>を比較することによって外部回路との接続とボードレベルの配線がテストできる。                                                                                               |

| BYPASS                   | TDIピンとTDOピンの間に1ビットのバイパス・レジスタを配置することによって、デバ                                                                                                                                      |

| (1)                      | イスに通常の動作をさせながらBSTデータが指定したデバイスをバイパスして隣接したデバイスに同期転送されるようにすることができる。                                                                                                                |

| USERCODE                 | 32 ビットの USERCODE レジスタを選択し、このレジスタを TDI ピンと TDO ピンの間に<br>配置することによって、USERCODE が TDO にシリアルにシフト・アウトされるようにす<br>ることができる。                                                               |

| IDCODE                   | IDCODE レジスタを選択し、これを TDI ピンと TDO ピンの間に配置することによって、IDCODE が TDO にシリアルにシフト・アウトされるようにすることができる。                                                                                       |

| ICR関連インストラクション           | JTAGポートを使用して、MasterBlaster <sup>TM</sup> またはByteBlasterMV <sup>TM</sup> ダウンロード・ケーブル、あるいは Jam Fileまたは Jam Byte-Code Fileを採用したエンベデッド・プロセッサから、APEX 20K デバイスをコンフィギュレーションするときに使用される。 |

| SignalTap関連<br>インストラクション | SignalTap エンベデッド・ロジック・アナライザでデバイス内部の動作をモニタするとき<br>に使用される。                                                                                                                        |

#### 注:

(1) EP20K1500EはBYPASSモードのJTAG動作のみをサポートしています。

APEX 20K デバイスのインストラクション・レジスタの長さは、10 ビットです。また、APEX 20K デバイスの USERCODE レジスタの長さは 32 ビットです。表 20 と 21 は、各 APEX 20K デバイスのバウンダリ・スキャン・レジスタの長さと IDCODE を示したものです。

| 表 20. APEX 20K デバイスのバウン | <i>・</i> ダリ・スキャン・レジスタの長さ |

|-------------------------|--------------------------|

| デバイス名                   | バウンダリ・スキャン・レジスタの長さ       |

| EP20K30E                | 420                      |

| EP20K60E                | 624                      |

| EP20K100                | 786                      |

| EP20K100E               | 774                      |

| EP20K160E               | 984                      |

| EP20K200                | 1,176                    |

| EP20K200E               | 1,164                    |

| EP20K300E               | 1,266                    |

| EP20K400                | 1,536                    |

| EP20K400E               | 1,506                    |

| EP20K600E               | 1,806                    |

| EP20K1000E              | 2,190                    |

| EP20K1500E              | 1 (1)                    |

### 注:

(1) このデバイスはJTAGバウンダリ・スキャン・テストをサポートしていません。

| 表 21. APEX 20 | Kデバイスの32        | !ビットIDCODE          |                |          |  |  |  |

|---------------|-----------------|---------------------|----------------|----------|--|--|--|

| デバイス名         |                 | IDCODE(32ビット)(1)    |                |          |  |  |  |

|               | バージョン<br>(4ビット) | パート番号(16 ビット)       | メーカのID(11 ビット) | 1 (1ビット) |  |  |  |

| EP20K30E      | 0000            | 1000 0000 0011 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K60E      | 0000            | 1000 0000 0110 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K100      | 0000            | 0000 0100 0001 0110 | 000 0110 1110  | 1        |  |  |  |

| EP20K100E     | 0000            | 1000 0001 0000 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K160E     | 0000            | 1000 0001 0110 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K200      | 0000            | 0000 1000 0011 0010 | 000 0110 1110  | 1        |  |  |  |

| EP20K200E     | 0000            | 1000 0010 0000 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K300E     | 0000            | 1000 0011 0000 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K400      | 0000            | 0001 0110 0110 0100 | 000 0110 1110  | 1        |  |  |  |

| EP20K400E     | 0000            | 1000 0100 0000 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K600E     | 0000            | 1000 0110 0000 0000 | 000 0110 1110  | 1        |  |  |  |

| EP20K1000E    | 0000            | 1001 0000 0000 0000 | 000 0110 1110  | 1        |  |  |  |

### 注:

- (1)

- 左側が最上位ビット (MSB) です。 IDCODEの最下位ビット (LSB) は常に1です。

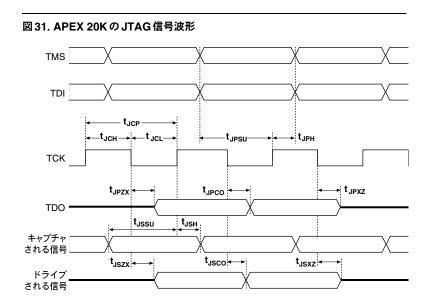

図31はJTAG信号に対するタイミングの規格を示したものです。

表22はAPEX 20KデバイスのJTAG信号のタイミング・パラメータとその値を示しています。

| 表22. AF           | 表 22. APEX 20K デバイスの JTAG 信号のタイミング・パラメータと値 |     |    |    |  |  |  |  |

|-------------------|--------------------------------------------|-----|----|----|--|--|--|--|

| シンボル              | パラメータ                                      | 最小  | 最大 | 単位 |  |  |  |  |

| t <sub>JCP</sub>  | TCK クロックの期間                                | 100 |    | ns |  |  |  |  |

| t <sub>JCH</sub>  | TCK クロックの High 時間                          | 50  |    | ns |  |  |  |  |

| t <sub>JCL</sub>  | TCK クロックの Low 時間                           | 50  |    | ns |  |  |  |  |

| t <sub>JPSU</sub> | JTAG ポートのセットアップ・タイム                        | 20  |    | ns |  |  |  |  |

| t <sub>JPH</sub>  | JTAG ポートのホールド・タイム                          | 45  |    | ns |  |  |  |  |

| t <sub>JPCO</sub> | JTAG ポートの「Clock-to-Output」遅延               |     | 25 | ns |  |  |  |  |

| t <sub>JPZX</sub> | JTAG ポートのハイ・インピーダンスから有効出力まで                |     | 25 | ns |  |  |  |  |

| t <sub>JPXZ</sub> | JTAG ポートの有効出力からハイ・インピーダンスまで                |     | 25 | ns |  |  |  |  |

| t <sub>JSSU</sub> | キャプチャ・レジスタのセットアップ・タイム                      | 20  |    | ns |  |  |  |  |

| t <sub>JSH</sub>  | キャプチャ・レジスタのホールド・タイム                        | 45  |    | ns |  |  |  |  |

| t <sub>JSCO</sub> | アップデート・レジスタの「Clock-to-Output」遅延            |     | 35 | ns |  |  |  |  |

| t <sub>JSZX</sub> | アップデート・レジスタのハイ・インピーダンスから有<br>効出力まで         |     | 35 | ns |  |  |  |  |

| t <sub>JSXZ</sub> | アップデート・レジスタの有効出力からハイ・インピー<br>ダンスまで         |     | 35 | ns |  |  |  |  |

詳細については、下記の資料をご覧ください。

- アプリケーション・ノート、AN 39「IEEE Std.1149.1 (JTAG) Boundary-Scan Testing in Altera Devices」

- Jam Programming & Test Language Specification

# デバイスの テスト

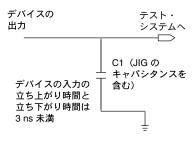

APEX 20K ファミリの各デバイスには機能テストが実施されており、その動作が保証されています。コンフィギュレーションされる各 SRAM(Static Random Access Memory)ビットとすべての論理機能は完全にテストされ、100%のコンフィギュレーションが保証されています。APEX 20K デバイスの AC テストは、図32 に等価な条件で行われています。デバイスのコンフィギュレーションとテストには、生産フローの中のあらゆる工程で複数のテスト・パターンが使用されています。

#### 図 32. APEX 20KのACテスト条件

電源トランジェントが AC 特性の測定に影響を及ぼすことがあります。正確な測定を行うため、複数の出力を同時に変化させることは避けてください。スレッショルドのテストは AC の測定条件では行わないでください。デバイスの出力が負荷のキャパシタンスをディスチャージするとき、大振いで発生します。これらのトランジェントシステムのグランド・ピンとテスト・ステムのグランドとの間に存在する寄マーンダクタンスに流れると、ノイズ・マージンが著しく低下します。

## 動作条件

表 23 から 26 は、2.5 V 動作の APEX 20K デバイスの絶対最大定格、推奨動作条件、DC 特性、およびキャパシタンスを示したものです。

| 表 23. API          | 表 23. APEX 20K デバイスの絶対最大定格 注 (1) |                                   |       |     |     |  |  |  |

|--------------------|----------------------------------|-----------------------------------|-------|-----|-----|--|--|--|