#### 2048-word × 8-bit Line Memory

The HM63021 is a 2048-word  $\times$  8-bit static serial access memory (SAM) with separate data inputs and outputs. Since it has an internal address counter, no external address signal is required and internal addresses are scanned serially. Using five different address scan modes, it is applicable to FIFO memories, double-speed conversions, 1H delay lines, and 1H/2H delay lines for digital TV signals. Its minimum cycle times are 28 ns and 34 ns, corresponding to 8 fsc of PAL TV and NTSC TV signals. All inputs and outputs are TTL-compatible.

#### **Features**

- · Five modes for various applications

- Corresponds to digital TV system with 4 fsc sampling (PAL, NTSC)

- Decoder signal output pin (fewer external circuits)

- · Asynchronous read/write operation

- Separate address counters for read/write

- No address input required

- High speed (cycle time 28/34/45 ns (min))

- Completely static memory (no refresh required)

- 8-bit SAM with separate I/O

- Low power (250 mW typ active)

- Single 5 V supply

- TTL compatible

#### **Ordering Information**

| Type No.     | Cycle<br>Time | Package              |

|--------------|---------------|----------------------|

| HM63021P-28  | 28 ns         | 300-mil, 28-pin      |

| HM63021P-34  | 34 ns         | plastic DIP (DP-28N) |

| HM63021P-45  | 45 ns         | _                    |

| HM63021FP-28 | 28 ns         | 28-pin plastic SOP   |

| HM63021FP-34 | 34 ns         | −(FP-28DA)           |

| HM63021FP-45 | 45 ns         | _                    |

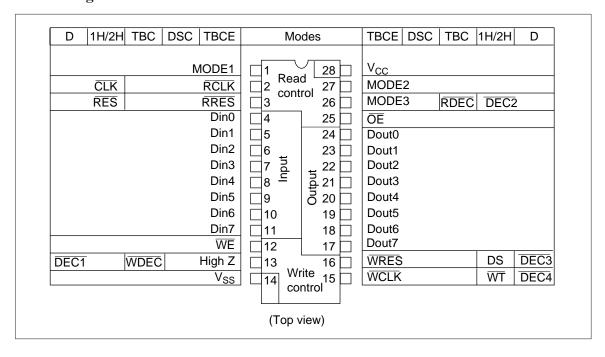

#### **Pin Arrangement**

## **HM63021 Series**

## **Pin Description**

| Pin Name         | Functions                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| MODE1            | Mode input 1 (all modes)                                                                                                        |

| RCLK/CLK         | Read clock input (TBCE, DSC, TBC) Clock input (1H/2H, D)                                                                        |

| RRES/RES         | Read reset input (TBCE, DSC, TBC) Reset input (1H/2H, D)                                                                        |

| Din 0 to Din 7   | Data inputs (all modes)                                                                                                         |

| WE               | Write enable input (all modes)                                                                                                  |

| High-Z/WDEC/DEC1 | High impedance (TBCE, DSC) Write decode pulse output (TBC) Decode pulse output 1 (1H/2H, D)                                     |

| Vss              | Ground (all modes)                                                                                                              |

| WCLK/WT/DEC4     | Write clock input (TBCE, DSC, TBC) Write timing input (1H/2H) Decode pulse output 4 (D)                                         |

| WRES/DS/DEC3     | Write reset input (TBCE, DSC, TBC) Delay select input (1H/2H) Decode pulse output 3 (D)                                         |

| Dout 0 to Dout 7 | Data outputs (all modes)                                                                                                        |

| ŌĒ               | Output enable input (all modes)                                                                                                 |

| MODE3/RDEC/DEC2  | Mode input 3 (TBCE) Read decode pulse output (TBC) Decode pulse output 2 (1H/2H, D)                                             |

| MODE2            | Mode input 2 (all modes)                                                                                                        |

| Vcc              | Power supply (+5 V) (all modes)                                                                                                 |

|                  | MODE1 RCLK/CLK RRES/RES Din 0 to Din 7 WE High-Z/WDEC/DEC1  Vss WCLK/WT/DEC4  WRES/DS/DEC3  Dout 0 to Dout 7 OE MODE3/RDEC/DEC2 |

### **Mode Table**

#### **Mode Signals**

| MODE1 | MODE2 | MODE3 | Mode                                   | Application Example |

|-------|-------|-------|----------------------------------------|---------------------|

| Н     | Н     | Н     | Time base compression/expansion (TBCE) | Picture in picture  |

| Н     | Н     | L     | Double speed conversion (DSC)          | Non interlace       |

| Н     | L     | *1    | Time base correction (TBC)             | Time base corrector |

| L     | Н     | *1    | 1H/2H delay (1H/2H)                    | Vertical filter     |

| L     | L     | *1    | Delay line (D)                         | Delay line          |

Note: 1. Decoder output signal (RDEC, DEC2)

### HM63021 Series

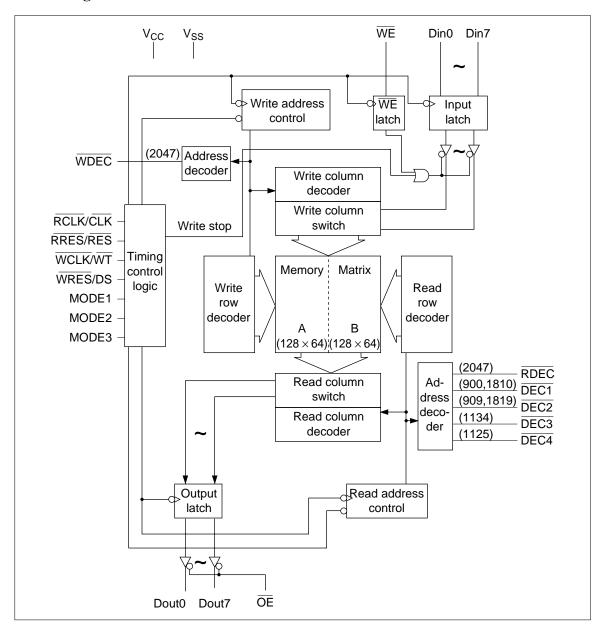

#### **Block Diagram**

### **HM63021 Series**

### **Absolute Maximum Ratings**

| Parameter                                      | Symbol | Rating              | Unit |

|------------------------------------------------|--------|---------------------|------|

| Voltage on any pin relative to V <sub>SS</sub> | VT     | $-0.5^{*1}$ to +7.0 | V    |

| Power dissipation                              | PT     | 1.0                 | W    |

| Operating temperature                          | Topr   | 0 to +70            | °C   |

| Storage temperature                            | Tstg   | -55 to +125         | °C   |

| Storage temperature under bias                 | Tbias  | -10 to +85          | °C   |

Note: 1. -3.5 V for pulse width  $\leq 10$  ns.

## **Recommended DC Operating Conditions** (Ta = 0 to +70 °C)

| Parameter      | Symbol | Min               | Тур | Max | Unit |

|----------------|--------|-------------------|-----|-----|------|

| Supply voltage | Vcc    | 4.5               | 5.0 | 5.5 | V    |

|                | Vss    | 0                 | 0   | 0   | V    |

| Input voltage  | ViH    | 2.4               | _   | 6.0 | V    |

|                | VIL    | -0.5 <sup>*</sup> | _   | 0.8 | V    |

Note: -3.0 V for pulse width  $\leq 10 \text{ ns}$ .

#### **DC** and Operating Characteristics (Ta = 0 to $+70^{\circ}$ C, $V_{CC} = 5 \text{ V} \pm 10\%$ , $V_{SS} = 0 \text{ V}$ )

| Parameter              | Symbol          | Min | Typ *1 | Max | Unit  | Test Condition                      |

|------------------------|-----------------|-----|--------|-----|-------|-------------------------------------|

| Input leakage current  | I <sub>LI</sub> | _   | _      | 10  | μΑ    | V <sub>CC</sub> = 5.5 V             |

|                        |                 |     |        |     |       | Vin = Vss to Vcc                    |

| Output leakage current | ILO             | _   | _      | 10  | μΑ    | OE = VIH                            |

|                        |                 |     |        |     |       | Vout = Vss to Vcc                   |

| Operating power        | Icc             | _   | 50     | 90  | mΑ    | Min. cycle, lout*2 = 0 mA           |

| supply current         |                 |     |        |     |       |                                     |

| Output voltage         | VoL             | _   | _      | 0.4 | V     | I <sub>OL</sub> = 8 mA *3 Dout 0 to |

|                        |                 |     |        |     |       | Dout 7, DEC output pin              |

|                        | Voh             | 2.4 | _      | _   | V     | $I_{OH} = -4$ mA, Dout 0 to Dout 7  |

|                        |                 |     |        |     |       | pin                                 |

|                        | 2.4             | _   | _      | V   | Іон = | -1 mA, DEC output pin               |

Notes: 1. Typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_a = 25^{\circ}\text{C}$  and for reference only.

- 2. Dout and DEC

- 3.  $I_{OL} = 6$  mA for 45 ns version.

## **Capacitance** (Ta = 25 °C, f = 1.0 MHz)

| Parameter             | Symbol | Min | Тур | Max | Unit | Conditions |

|-----------------------|--------|-----|-----|-----|------|------------|

| Input capacitance     | Cin    | _   | _   | 6   | pF   | Vin = 0 V  |

| Output capacitance *2 | Cout   | _   | _   | 9   | pF   | Vout = 0 V |

Notes: 1. These parameters are sampled and not 100% tested.

2. 13, 15–24, 26 pin

#### **HM63021 Series**

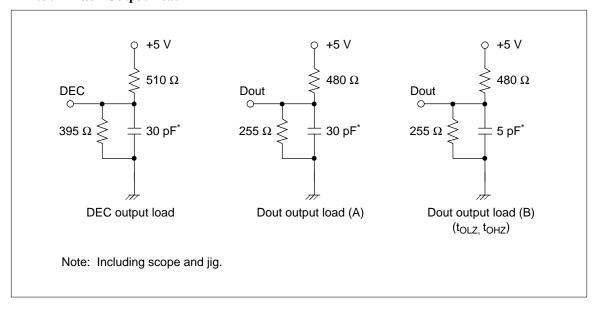

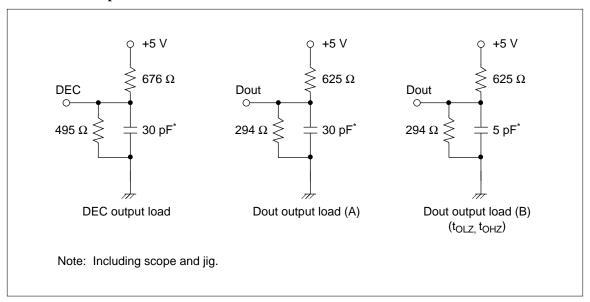

AC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $T_a = 0 \text{ to } +70^{\circ}\text{C}$ , unless otherwise noted)

#### **AC Test Conditions:**

• Input and output timing reference levels: 1.5 V

Input pulse levels: V<sub>SS</sub> to 3 V

Input rise and fall times: 5 ns

#### HM63021-28/34 Output Load

#### HM63021-45 Output Load

HM63021 Series

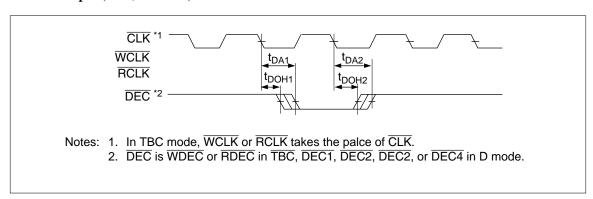

## Read Cycle

|                                    |        |                   | HM63 | 021-28 | HM63 | 3021-34 | HM63 | 3021-45 |      |

|------------------------------------|--------|-------------------|------|--------|------|---------|------|---------|------|

| Parameter                          |        | Symbol            | Min  | Max    | Min  | Max     | Min  | Max     | Unit |

| Read cycle time                    |        | t <sub>RC</sub>   | 28   | _      | 34   | _       | 45   | _       | ns   |

| Read clock width                   |        | t <sub>RWL</sub>  | 10   | _      | 10   | _       | 15   | _       | ns   |

|                                    |        | trwh              | 10   | _      | 10   | _       | 15   | _       | ns   |

| Access time                        | (fall) | tAC               | _    | 20     | _    | 25      | _    | 30      | ns   |

|                                    | (rise) | t <sub>DA1</sub>  | _    | 20     | _    | 25      | _    | 30      | ns   |

| Decode output access               | s time | t <sub>DA2</sub>  | _    | 40     | _    | 50      | _    | 60      | ns   |

| Output hold time                   |        | tон               | 5    | _      | 5    | _       | 5    | _       | ns   |

| Decode output hold                 | (fall) | tDOH1             | 5    | _      | 5    | _       | 5    | _       | ns   |

| time                               | (rise) | t <sub>DOH2</sub> | 5    | _      | 5    | _       | 5    | _       | ns   |

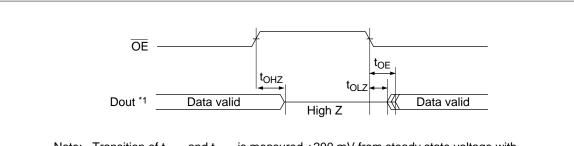

| Output enable access time          |        | toe               | _    | 20     | _    | 25      | _    | 30      | ns   |

| Output disable to output in high Z |        | tonz              | 0    | 15     | 0    | 20      | 0    | 25      | ns   |

| Output enable to output in low Z   |        | tolz              | 5    | _      | 5    | _       | 5    | _       | ns   |

| Input rise and fall time           | )      | t⊤                | 3    | 50     | 3    | 50      | 3    | 50      | ns   |

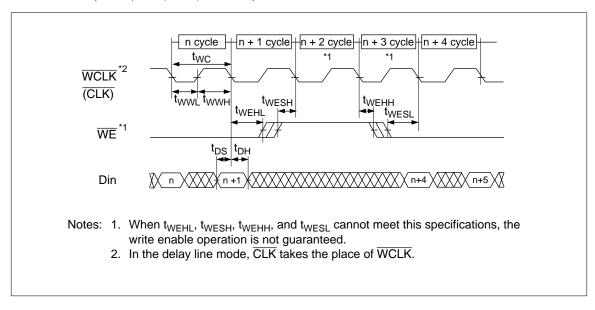

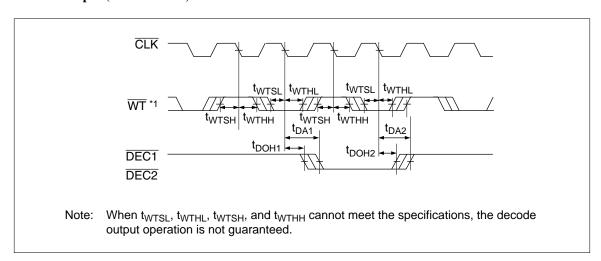

## Write Cycle

|                          |                  | HM63021-28 |     | HM63021-34 |     | HM63021-45 |     |      |

|--------------------------|------------------|------------|-----|------------|-----|------------|-----|------|

| Parameter                | Symbol           | Min        | Max | Min        | Max | Min        | Max | Unit |

| Write cycle time         | twc              | 28         | _   | 34         | _   | 45         | _   | ns   |

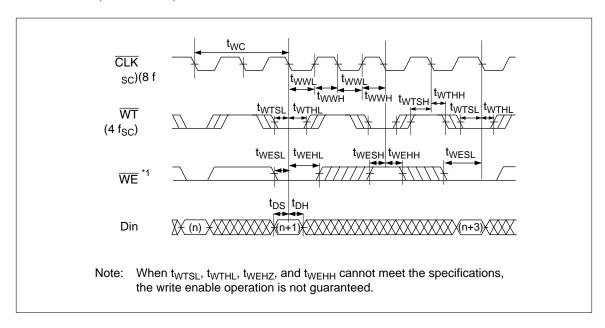

|                          | twc (1H/2H Mode) | 56         | _   | 68         | _   | 90         | _   | ns   |

| Write clock width        | tww∟             | 10         | _   | 10         | _   | 15         | _   | ns   |

|                          | twwn             | 10         | _   | 10         | _   | 15         | _   | ns   |

| Input data setup time    | tos              | 5          | _   | 5          | _   | 7          | _   | ns   |

| Input data hold time     | tDH              | 5          | _   | 5          | _   | 7          | _   | ns   |

| WE setup time            | twesl            | 5          | _   | 5          | _   | 7          | _   | ns   |

|                          | twesh            | 5          | _   | 5          | _   | 7          | _   | ns   |

| WE hold time             | twehl            | 5          | _   | 5          | _   | 7          | _   | ns   |

|                          | twehh            | 5          | _   | 5          | _   | 7          | _   | ns   |

| WT setup time            | twtsl            | 5          | _   | 5          | _   | 7          | _   | ns   |

|                          | twrsh            | 5          |     | 5          | _   | 7          | _   | ns   |

| WT hold time             | twthl            | 5          | _   | 5          | _   | 7          | _   | ns   |

|                          | twтнн            | 5          | _   | 5          | _   | 7          | _   | ns   |

| Input rise and fall time | t⊤               | 3          | 50  | 3          | 50  | 3          | 50  | ns   |

#### **Mode Description**

Time Base Compression/Expansion Mode: Turns the HM63021 into a 2048-word × 8-bit FIFO memory with asynchronous input/output. The HM63021 provides 2 clocks (RCLK, WCLK) and 2 resets for read and write (RRES, WRES). The internal address counters increment by 1 address clock and are reset to address 0. A write-inhibit function of the HM63021 stops writing automatically after the data has been written into all addresses 0 to 2047. The write-inhibit function is released by reset using WRES, and the HM63021 restarts writing into address 0.

**Double-Speed Conversion Mode:** Turns the HM63021 into a 1024-word  $\times$  8-bit  $\times$  2 memory with asynchronous input/output. It is used for generating non-interlaced TV signals. When the original signal and the interpolated signal (1 field delay) of interlaced signals are input to the HM63021, multiplexed per dot, it outputs non-interlaced signals for each line. 8 fsc should be input to  $\overline{RCLK}$  and  $\overline{WCLK}$ . A standard H synchronizing signal and a non-interlace H synchronizing signal are input to  $\overline{WRES}$  and  $\overline{RRES}$  respectively. A write-inhibit function is provided in this mode, making it applicable to PAL TV, where extra data (1135–1024 = 111 bits) is ignored.

**TBC Mode:** Turns the HM63021 into 2048-word  $\times$  8-bit FIFO memory with asynchronous input/output. The HM63021 provides 2 clocks (RCLK, WCLK) and 2 resets (RRES, WRES), one each for read and write. The internal address counters increment by 1 address at each clock and are reset to address 0. The internal address counters return to address 0 after they reach address 2047.

The HM63021 outputs a write decode pulse from  $\overline{\text{WDEC}}$ , synchronizing it with address 2047 in the write address counter, and read a decode pulse from  $\overline{\text{RDEC}}$ , synchronizing with address 2047 in the read address counter. Using these pulses, the memory area can be extended easily (multiple-HM63021s can be used with ease).

**1H/2H Delay Mode:** Turns the HM63021 into a 1024-word  $\times$  8-bit  $\times$  2 delay line with synchronous input/output. Delay time is defined by the reset period of  $\overline{RES}$ . Since the HM63021 outputs a 901 decode pulse ( $\overline{DEC1}$ ) and a 910 decode pulse ( $\overline{DEC2}$ ), connecting  $\overline{DEC2}$  to  $\overline{RES}$ , for example, outputs 1H- and 2H- delayed signals alternately at an 8-fsc cycle when the original signal is input at a 4-fsc cycle. A write-inhibit function is provided in this mode, making it applicable to PAL TV, where extra data (1135–1024 = 111 bits) is ignored.

**Delay Line Mode:** Turns the HM63021 into a 2048-word  $\times$  8-bit delay line with synchronous input/output. Delay time (3 to 2048 bits) is defined by the reset period of  $\overline{RES}$ . The delay is 2048 bits when  $\overline{RES}$  is fixed high. Signals delayed by 910 bits to 1135 bits for example, can be easily obtained without external circuits by just connecting selected decoded pulses on  $\overline{DEC1}$ - $\overline{DEC4}$  to  $\overline{RES}$ .

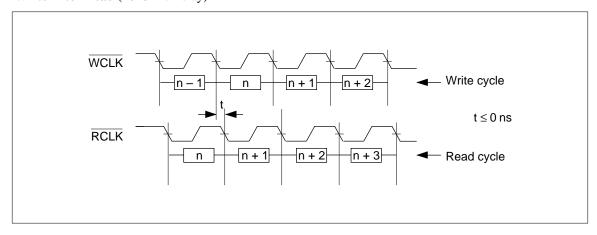

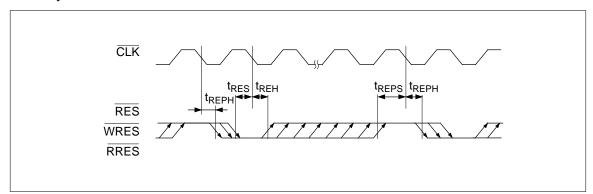

#### **Reset Cycle**

|                               |                   | HM63 | 021-28 | HM63 | 021-34 | HM63 | 021-45 |      |

|-------------------------------|-------------------|------|--------|------|--------|------|--------|------|

| Parameter                     | Symbol            | Min  | Max    | Min  | Max    | Min  | Max    | Unit |

| Reset setup time              | t <sub>RES</sub>  | 8    | _      | 9    | _      | 10   | _      | ns   |

| Reset hold time               | t <sub>REH</sub>  | 5    | _      | 5    | _      | 7    | _      | ns   |

| Clock setup time before reset | t <sub>REPS</sub> | 8    | _      | 9    | _      | 10   | _      | ns   |

| Clock hold time before reset  | tREPH             | 5    | _      | 5    | _      | 7    | _      | ns   |

| Input rise and fall time      | t⊤                | 3    | 50     | 3    | 50     | 3    | 50     | ns   |

7

#### Notes on Using HM63021:

- Hitachi recommends that pin 13 (high impedance) should be fixed by pulling up or down with a resistor (of several  $k\Omega$ ) in TBC or DSC mode.

- Hitachi recommends that the mode signal input pins and DS pin should be fixed by pulling them up or down with a resistor (of several kΩ).

- Data integrity cannot be guaranteed when mode or DS is changed during operation.

- When a read address coincides with a write address in TBCE, TBC, or DSC mode, the data is written correctly but it is not always read correctly.

- At power on, the output of the address counter is not defined. Therefore, operations before the system is reset cannot be guaranteed, and the decode signal output is not defined until after the first reset cycle.

- The decode signal is latched by a decode output latch circuit at the previous address of the internal counter address and is output-synchronized with the next address. For example, WDEC in TBC mode is latched at write address 2046 and is output at write address 2047. If a write reset is performed on address 2047 at this time, the write address becomes 0 and WDEC is output. The same operation is performed in other modes.

- When TBC or DSC or TBCE mode is used, at least one RCLK dummy cycle is required before starting write operation (before executing write pre-reset cycle) after power up.

- Transition time of input level  $t_T$  is defined as the rising time from  $V_{IL}$  to  $V_{IH}$  and the falling time from  $V_{IH}$  to  $V_{IL}$ .

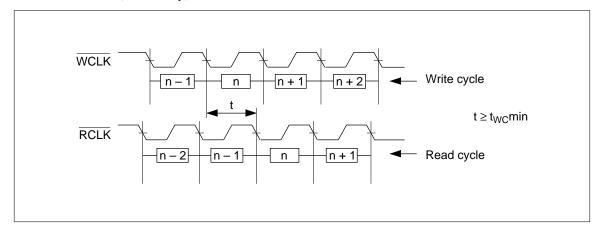

#### **Read After Write** (3 Bit Delay)

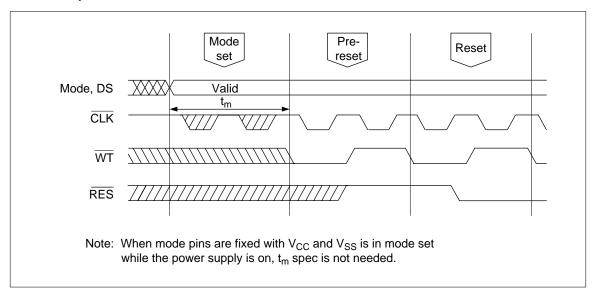

- In the reset cycle, the input levels of WRES, RRES, and RES are raised to satisfy t<sub>REH</sub>, and are fixed high until t<sub>REPH</sub> in the next pre-reset cycle is satisfied. The rise timings of the reset signals (RES, WRES, RRES) are optional provided that the t<sub>REPS</sub> specification is satisfied. The timings at which RES, WRES, and RRES fall after pre-reset are also optional, provided that the t<sub>REPH</sub> and t<sub>RES</sub> specifications are satisfied.

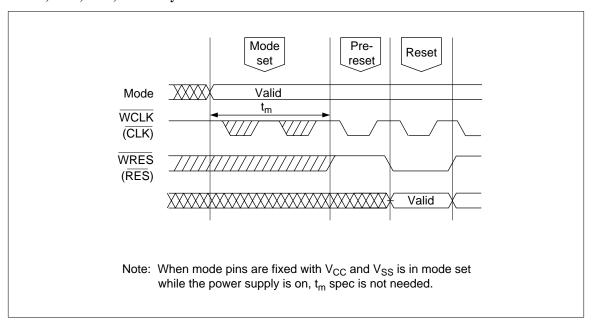

- Hitachi recommends that t<sub>m</sub> (time between mode set and the first cycle (pre-reset)) should be kept for 2 cycle times (56 ns/68 ns/90 ns) or more while the power supply is on.

#### Write After Read (2048 Bit Delay)

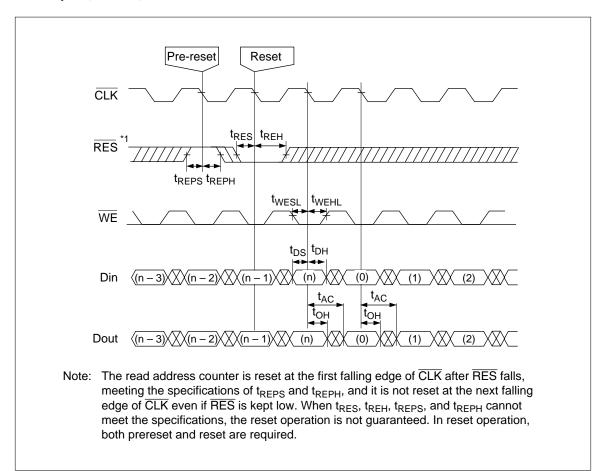

#### **Reset Cycle**

#### TBCE, TBC, DSC, and Delay Line Mode

#### 1H/2H Delay Mode

### **Decode Signal**

When internal address counter reaches the specified address as shown below, decode outputs become low.

| Mode       | Pin No. | Pin Name | Internal<br>Address | Output Signal<br>Timing | Operation                                                                                                                      |

|------------|---------|----------|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| TBC        | 13      | WDEC     | Write 2047          | After write 2047        | Completion of writing on all bits is detected.                                                                                 |

|            | 26      | RDEC     | Read 2047           | Output of 2046          | Completion of reading from all bits is detected.                                                                               |

| 1H/2H      | 13      | DEC1     | Read 900 (2H)       | Output of 900 (1H)      | By inputting this signal to pin number 3, a 901/1802-bit delay output is obtained.                                             |

|            | 26      | DEC2     | Read 909 (2H)       | Output of 909 (1R)      | By inputting this signal to pin number 3, a 910/1820-bit delay output is obtained.                                             |

| Delay line | 13      | DEC1     | Read 900            | Output of 899           | By inputting this signal to pin number 3, a 901-bit delay output is obtained.                                                  |

|            |         |          | Read 1810           | Output of 1809          | By inputting this signal to pin number 3 after the frequency of DEC1 is divided into two, 1811-bit delay outputs are obtained. |

|            | 26      | DEC2     | Read 909            | Output of 908           | By inputting this signal to pin number 3, a 910-bit delay output is obtained.                                                  |

|            |         |          | Read 1819           | Output of 1818          | By inputting this signal to pin number 3 after the frequency of DEC2 is divided into two, 1820-bit delay outputs are obtained. |

|            | 16      | DEC3     | Read 1134           | Output of 1133          | By inputting this signal to pin number 3, 1135-bit delay output is obtained.                                                   |

|            | Ī5      | DEC4     | Read 1125           | Output of 1124          | By inputting this signal to pin number 3, 1126-bit delay output is obtained.                                                   |

Note: When the counter is reset by a reset signal (RRES, RES, WRES), the address becomes 0.

11

#### **Write-Inhibit Function**

When internal address counter is as follows, writing is inhibited automatically for the next

cycle. The write-inhibit function is canceled by reset through  $\overline{WRES}$  or  $\overline{RES}$ .

| Mode  | Write-Inhibit Function (Internal Counter Address) |

|-------|---------------------------------------------------|

| TBCE  | Write-inhibit after address 2047                  |

| DSC   | Write-inhibit after address 1023 × 2              |

| TBC   | No function                                       |

| 1H/2H | Write-inhibit after address 1023                  |

| D     | No function                                       |

Note: When address counter is reset by WRES or RES, the address becomes 0.

#### **Timing Waveforms**

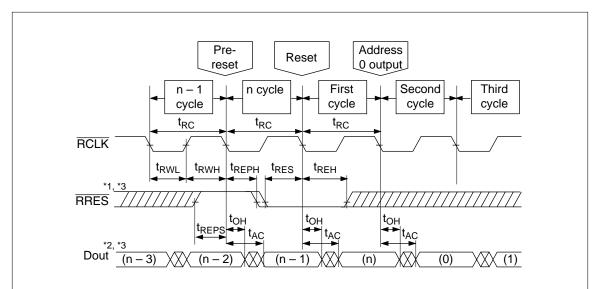

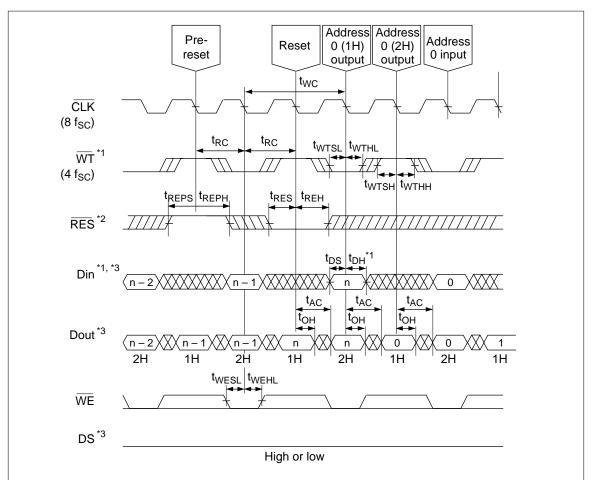

#### Read Reset Cycle (TBCE, TBC Modes)

Notes: 1. The read address counter is reset at the first falling edge of  $\overline{RCLK}$  after  $\overline{RRES}$  falls, meeting the specifications of  $t_{REPS}$ , and  $t_{REPH}$ , and it is not reset at the next falling edge of  $\overline{RCLK}$  even if  $\overline{RRES}$  is kept low. When  $t_{RES}$ ,  $t_{REH}$ ,  $t_{REPS}$ , and  $t_{REPH}$  cannot meet the specifications, the reset operation is not guaranteed. In reset operation, both prereset and reset are required.

- 2. Output is from the read address of the previous cycle.

- 3. When RRES is fixed high, the data at the read address counter is reset after the data of address 2047 is output, and the same operation restarts.

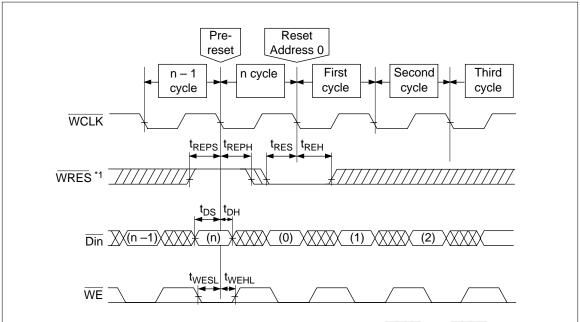

Write Reset Cycle (TBCE, TBC Modes)

Note: The write address counter is reset at the first falling edge of WCLK after WRES falls, meeting the specifications of t<sub>REPS</sub> and t<sub>REPH</sub>, and it is not reset at the next falling edge of WCLK even if WRES is kept low. When t<sub>RES</sub>, t<sub>REH</sub>, t<sub>REPS</sub>, and t<sub>REPH</sub> cannot meet the specifications, the reset operation is not guaranteed. In reset operation, both prereset and reset are required.

13

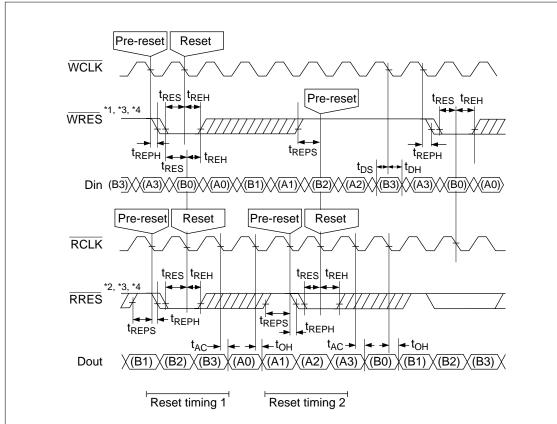

Reset Cycle (DSC Modes)

- Notes: 1. The write address counter is reset at the first falling edge of WCLK after WRES falls, meeting the specifications of t<sub>REPS</sub> and t<sub>REPH</sub>, and is not reset at the next falling edge of WCLK even if WRES is kept low. When t<sub>RES</sub>, t<sub>REH</sub>, and t<sub>REPH</sub> cannot meet the specifications, the reset operation is not guaranteed.

- The read address counter is reset at the first falling edge of RCLK after RRES falls, meeting the specifications of t<sub>REPS</sub> and t<sub>REPH</sub>, and it is not reset at the next falling edge of RCLK even if RRES is kept low. When t<sub>RES</sub>, t<sub>REH</sub>, t<sub>REPS</sub>, and t<sub>REPH</sub> cannot meet the specifications, reset operation is not guaranteed.

- 3. When t<sub>REPH</sub>, t<sub>RES</sub>, t<sub>REH</sub> (WRES to WCLK), t<sub>RES</sub>, t<sub>REH</sub>, (WRES to RCLK) or t<sub>REPS</sub>, t<sub>REPH</sub>, t<sub>RES</sub>, t<sub>REH</sub> (RRES to RCLK) cannot meet the specifications, the output of video signal A is not guaranteed (reset timing 1).

- When t<sub>REPS</sub> (WRES to RCLK), or t<sub>RES</sub>, t<sub>REH</sub>, t<sub>REPS</sub>, t<sub>REPH</sub> (RRES to RCLK) cannot meet the specifications, the interpolation signal B is not guaranteed (reset timing 2).

#### Reset Cycle (1H/2H Modes)

Notes: 1.  $\overline{WT}$  is the input during half cycle of  $\overline{CLK}$ , meeting the specifications of  $t_{WTSL}$ ,  $t_{WTHL}$ ,  $t_{WTSH}$ , and  $t_{WTHH}$ . Data is written when  $\overline{WT}$  is low. Reset is possible when  $\overline{WT}$  is high.

- Read address counter is reset at the first falling edge of CLK after RES falls, meeting the specifications of t<sub>REPS</sub> and t<sub>REPH</sub>, and it is not reset at the next falling edge of CLK even if RES is kept low. When t<sub>RES</sub>, t<sub>REH</sub>, t<sub>REPS</sub>, and t<sub>REPH</sub> cannot meet the specifications, the reset operation is not guaranteed. In reset operation, both prereset and reset are required.

- 3. When  $\overline{DS}$  is fixed high, 1H output date is delayed by n bits and 2H output data is delayed by 2n bits where 2n is the reset cycle of  $\overline{RES}$ . When  $\overline{DS}$  is fixed low, 1H output data is delayed by n-5 bits and 2H output data is delayed by 2n-5 bits.

#### Reset Cycle (D Modes)

#### Write Enable (TBCE, DSC, TBC, D Modes)

#### Write Enable (1H/2H Mode)

#### **Decode Output (TBC, D Modes)**

#### Decode Output (1H/2H Modes)

## HM63021 Series

#### Output Enable (All Modes)

Note: Transition of  $t_{OHZ}$  and  $t_{WLZ}$  is measured ±200 mV from steady state voltage with output load B. These parameters are sampled and not 100% tested.

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# HITACHI

#### Hitachi, Ltd.

Semiconductor & IC Div.

Karukozaka MN Bldg., 2-1, Ageba-cho, Shinjuku-ku, Tokyo 162, Japan

Tel: Tokyo (03) 3266-9376 Fax: (03) 3235-2548

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1835 U S A

Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Div. Continental Europe Hans-Pinsel-Str. 10a; D-85540 Haar bei München Postfach 1208; D-85530 Haar bei München Tel: 089-46 14-0 Fax: 089-46 31 51 Hitachi Europe Ltd.

Electronic Components Div.

Northern Europe Headquarters

Wihtebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA

United Kingdom

Tel: 0628-585000

Fax: 0628-778322

Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 0104 Tel: 535-2100 Fax: 535-1533

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsim Sha Tsui, Kowloon Hong Kong

Tel: 7359218 Fax: 7306071